# USB Type-C / DisplayPort 1.4 MST Hub (DSC)

#### **Features**

- USB Type-C DisplayPort Alt-mode de-mux

- ► Simultaneous USB3.2 Gen2 and 2 lanes DP1.4a input OR 4 lanes DP1.4a input

- ► Flip option for connector plug orientation

- ▶ DP lane swap and polarity swap

- DisplayPort® (DP) ver.1.4a compliant receiver

- ► Link rate 1.62 / 2.74 / 5.4 / 8.1Gbps

- ▶ 1, 2, or 4 lanes configuration

- ► MST up to 6 streams (compressed /uncompressed)

- ▶ FEC Decode

- ▶ DSC Transport & Decode

- ► AUX CH 1 Mbps

- ► HPD OUT

- ▶ Adaptive receiver equalization

- ▶ TPS4 EQ Phase LT support

- ▶ Scrambling of main link data

- De-spreading of link frequency

- Video Stream Handling

- RGB/ YCC 444/422/420 pixel format up to 16 bpc

- Up to 1080 Mpix/sec dual pixel path

- ▶ DPCD

- DPCD data structure revision 1.4

- DSC support capability & control

- FEC capability & control

- SST Split SDP capability

- VSC EXT SDP for VESA & CTA

- Protocol converter capability & control

- Virtual DP Peer Device capability & control

- CEC tunneling over AUX

- Chainable SDP packets (2KB or more metadata per stream)

- ► Adaptive Sync SDP

- ▶ PPS SDPAudio stream handling

- Non-HBR Compressed Formats

- 2/8 ch layouts

- Up to 192kHz sample rates

- Dolby Digital, Digital+, Atmos

- ▶ HBR Audio Formats

- 8 ch layout

- Up to 1536kHz sample rates

- Dolby TrueHD, Atmos, DTS Master

- LPCM Formats

- 2/8/16/32 Ch

- Up to 192kHz sample rates

- 3D LPCM, speaker allocation & mapping

- ▶ OneBit DSD Formats

- 2/8 ch

- Single & Double Rate

- 12288 kHz sample rates

- ▶ DST DSD Formats

- Single/Double rate

- Up to 22579.2kHz

- Audio InfoFrame/ ACP/ ISRC/ Audio Metadata DI packets

- Triple DP1.4a / HDMI2.0b (DP++) transmitters

- ▶ DP mode

- Lane count, Link rate conversion

- Link rate 1.62 / 2.74 / 5.4 / 8.1Gbps

- 1, 2, or 4 lanes configuration

- DSC stream transport with FEC Encode

- MST up to 6 streams (compressed / uncompressed)

- AUX CH 1 Mbps

- 3.3V HPD IN

- ► HDMI mode

- TX1 & TX3: VML AC coupled HDMI

- TX2: CML DC-coupled HDMI

- No External Level shifters needed

- 600 MHz maximum TMDS character clock

- TMDS character-clock divide\_by\_4 mode

- HPD\_IN (5V Tolerant)

- DDC CH (5V Tolerant)

- HDMI 2.1 Features

- ▶ Through 6GHz TMDS Mode

- Supports 4k120Hz,4:2:0, 8bpc with Adaptive Sync to VRR conversion

- Dynamic HDR Metadata through Extended Metadata Packet

- ► Supports VRR, FVA, QMS, QFT, ALLM

- ▶ Scrambler for DP/HDMI output

- Programmable signal amplitude and edge rate control

- ▶ Programmable pre-emphasis control

- ► Pixel format RGB / YCC 444/422/420

- ▶ Deep color up to 16 bits per color

- ▶ 3D video timings

- ► CEC support snooping, tunneling

- ▶ SCDC read request handling

- ► Metadata handling

- ▶ Conversion to DVI output

- ► Link power management

### Features (continued)

- USB3.2 compliant re-timer

- ▶ 5Gbps and 10Gbps support

- ► Spread spectrum clocking

- ▶ LFPS polling and processing

- ► Lane polarity inversion

- ▶ Bit level re-timer for SS mode

- SRIS (Separate Reference Clock Independent SSC) for SSP mode

- ▶ Adaptive Receiver Equalization

- ► Multi-tap FIR EQ Transmitter Emphasis

- Video processing

- ▶ MST to SST conversions or pass-through

- ► SST lef-right separation

- Color space conversion from RGB to YCC

- ► Colorimetry support: BT2020, BT709, BT601, and Adobe RGB

- Color bit depth expansion (10 to 12 bits) 16 bits per color pass through

- ▶ DP to HDMI Stereoscopic 3D Transport

- ► Frame sequential to stacked top-bottom conversion

- ▶ Pass through of other 3D formats

- ▶ Programmable coefficient 3x3 matrix

- Programmable input offset

- Programmable output offset

- Programmable output clipping levels

- ► Chroma down sampling

- 5-tap H & V FIR filters with programmable coefficients

- 12 bits per color input width

- 12 bits per color output width

- YCbCr444 to YCbCr420 conversion

- YCbCr444 to YCbCr422 conversion

- ▶ Pass through for YCbCr444/422/420

- ► Dual DSC1.2A stream decoding

- ► 1/2/4 Slice DSC1.2Aa RGB/YCC444/422/420 10-b format support

- ▶ FEC decoding / encoding

- ▶ Video Horizontal blanking expansion

- ▶ Pixel stream de-skewing

- ► Adaptive Sync Video

- Max video resolution and color depth on DP output uncompressed

- 5K3K60Hz, RGB/YCbCr444, 8 bpc

- 8K4K60Hz, YCbCr420 up to 8 bpc

- 4K2K120Hz, RGB/YCbCr444, 8 bpc

- Max video resolution and color depth on DP output compressed (DSC)

- 8K4K60Hz, RGB/YCC444 up to 8 bpc

- 5K3K60Hz, RGB/YCbCr444, 12 bpc

- 4x 4K2K60Hz, RGB/YCbCr444, 8 bpc

- Max video resolution and color depth on HDMI TX

- 4Kp60Hz, RGB/YCbCr444, 8 bpc

- 4Kp60Hz, YCbCr420, up to 16 bpc

- 4Kp30Hz, RGB/YCbCr444, up to 16 bpc

- Audio processing

- Audio stream forwarding from DP RX to HDMI TX

- ► Conversion to I2S or TDM audio output (8 CH)

- Conversion to SPDIF audio output (2CH)

- HDCP support

- ► HDCP1.3 to HDCP1.4 Repeater function

- ► HDCP2.3 to HDCP1.4 Repeater function

- ► HDCP2.3 to HDCP2.3 Repeater function

- ▶ Read- protected embedded HDCP keys

- Enhanced security

- ► Encrypted on-chip key storage

- ► RSA-2048bit signed application firmware

- ► Secure Boot & In-system Programming

- ► Test, debug ports deactivation

- Metadata handling

- ► HDMI TX DVI/HDMI mode setting (DPCD register)

- ► YCbCr444-420 conversion (DPCD register)

- ▶ IEC60958 BYTE3 channel status overwrite

- ► CTA861G INFO FRAME generation

- ► CTA861.3 HDR and Mastering InfoFrame

- ► Chainable VSC\_EXT SDP packing format

- ARM processor and peripheral controllers

- ARM Cortex M3 core

- ► SPI controller

- ▶ I2C master, slave controller

- ► On-Chip, RAM, ROM, OTP

- Device configuration options

- ▶ Application FW stored in SPI flash

- ▶ AUX CH, I2C host interface

- Internal video pattern generator

- Configurable through vendor specific DPCD registers

- EMI reduction support

- ▶ Spread spectrum for DP input, output

- ▶ Scrambler for DP and HDMI outputs

- · Low power operation

- ▶ 860mW nominal operation with retimer

- ▶ 700mW nominal operation without retimer

- ▶ Under 10mW Standby operation

- ESD specification

- ► ESD: ±2kV HBM, 500 V CDM

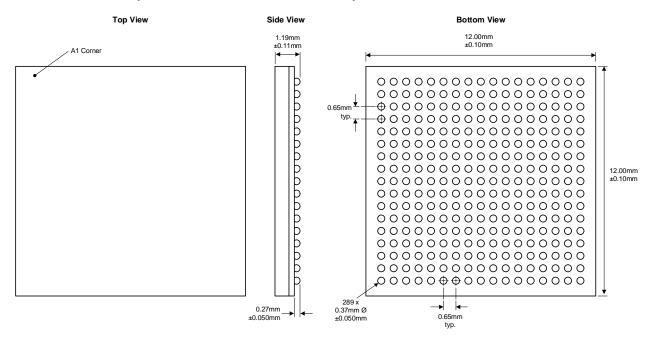

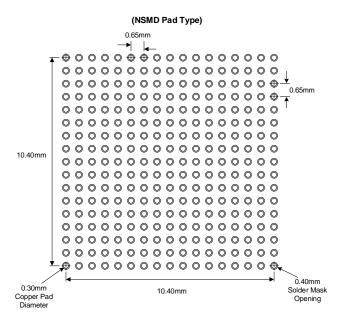

- Package

- ▶ 289 LFBGA (12 x 12mm)

- ► Halogen free Halogen free RoHS and Green Compliant

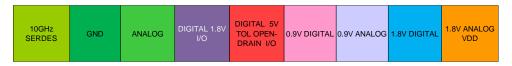

- Power supply voltages

- ▶ 1.8V Analog and I/O, 0.95V Analog and core

### Description

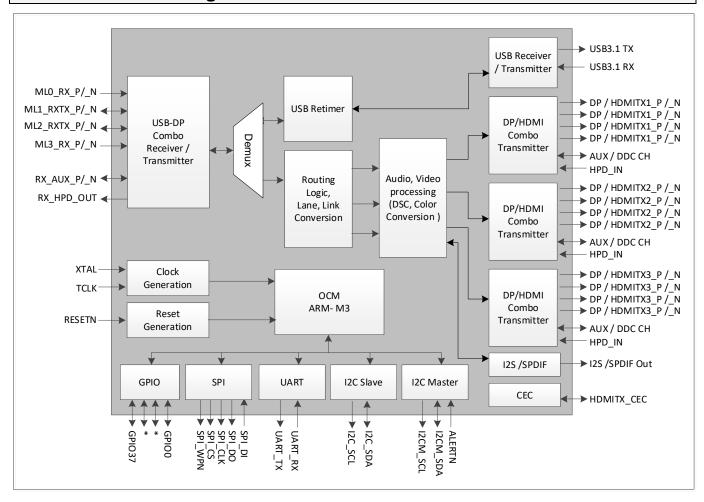

The KTM5030 is an advanced DisplayPort1.4a MST hub with an integrated USB type-C de-multiplexer, targeted primarily for Mobile Notebook accessory and display applications. This device functions as a multistream audio-video splitter and protocol converter with an HDCP1.x/ HDCP2.3 repeater supporting both compressed (DSC) and uncompressed AV streams.

KTM5030 has a DP alt-mode capable USB Type-C Upstream Facing Port (UFP). The four high speed lanes of UFP can receive DP1.4a MST audio-video and USB3.2 Gen2 data streams simultaneously. The input lane mapping is flexible and meets standard DP or the USB Type-C connector with flip orientation requirements. The incoming DP and USB signals are de-multiplexed, retimed, and transmitted on the Downstream Facing Ports (DFP). The KTM5030 consists of three AC coupled DP/DP++ or DC coupled HDMI/DVI DFPs, each with four high-speed lanes and one USB port with USB3.2 TX and RX pair. The Stream Routing Logic in KTM5030 allows flexible routing of incoming DP MST stream converted into any combination of MST or SST streams on any of the DFP video ports with link rate and lane count change option. Also, the SST stream can be replicated on two or more DFP ports. In addition, the DP SST stream can be converted into a HDMI or DVI output (TMDS signal format).

The combo receiver in KTM5030 supports all DP standard data rates up to HBR3 (8.1 Gbps/lane) and USB3.2 Gen1 (5.0 Gbps) and Gen2 (10.0 Gbps). The dual mode (DP++) transmitters support DP standard data rates up to 8.1 Gbps/lane and TMDS data rates up to 6.0 Gbps/lane. The side-band channel uses 1.0 Mbps Manchester-coded AUX signaling for DP and DDC signaling up to 100kbps for the HDMI interface.

KTM5030 is capable of processing up to six DP audiovideo streams compressed or uncompressed. FEC decoding and encoding is employed for the reliable reception and transmission of DSC1.2a compressed streams. These streams can be part of one single large video timing or six independent video timings from a single source with corresponding independent multi-channel audio. The highest video timing per stream and the number of streams transported is limited by the DP1.4a and HDMI2.0 link bandwidth. When the received DP MST stream is in DSC1.2a compressed format, KTM5030 can decode the

streams (max two streams) or pass through to the downstream sink or to another cascaded KTM5030 device. If a DP source sends an 8k4k60Hz RGB/YCC444 DSC1.2a encoded video as four 4k2k60Hz MST, then two KTM5030 devices are needed to decode all four streams. KTM5030 supports both RGB 444 and YCC444/422/420 video pixel encoding formats with a color depth up to 16 bpc (bits per component or 48 bits per pixel). It has a pixel processing unit capable of video pixel encoding format conversion from RGB444 to YCC444 with bit depth expansion and down scaling from YCC444 to YCC422/420. Pixel format conversion along with horizontal blanking expansion improves interoperability and smooth rendering of CVT video timings from a mobile PC on a consumer displays such as TVs and projectors which supports only CEA timings.

KTM5030 processes High Dynamic Range (HDR) video content specified in BT601, BT709, BT2020, BT2100 , Adobe RGB colorimetry format with the proper metadata conversion from DP to HDMI. It also offers secure reception and transmission of high bandwidth digital audio and video content with HDCP1.x or HDCP2.3 content protection. As a branch device KTM5030 functions as a HDCP1.x and HDCP2.3 repeater between the DP source and DP or HDMI sink.

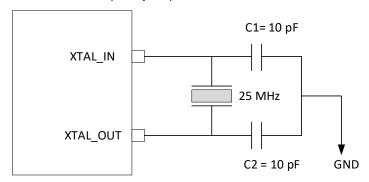

KTM5030 uses an external 25 MHz reference clock for its operation. The reference clock can be generated from a 25MHz crystal or from an external source. It has a 300MHz ARM Cortex M3 CPU with on-chip memories for code and data storage. The peripheral subsystem includes SPI, UART (debug only), and I2C master, slave interfaces. An internal Power-On Reset (POR) circuit senses the voltage on the reset input and provides the chip reset during system power-up. The KTM5030 uses an external 16 Mbit SPI flash memory for storing the RSA-2048 signed application firmware with fail-safe recovery. At boot up, the CPU goes through a secure boot process authenticating the application code image stored in the SPI flash. It supports both standard mode and quad mode SPI operation. Firmware update for the SPI flash is done securely through the DP AUX CH or I2C host interface (Secure In-System-Programming).

Kinetic Technologies Confidential

**Table 1. Part Numbers**

| Features              | KTM5030                      |

|-----------------------|------------------------------|

|                       | USB-C                        |

|                       | (DP alt-mode)                |

| Input                 | (DP 4 lanes OR               |

|                       | 2 lanes DP and               |

|                       | 2 lanes USB3.2)              |

|                       | 3x DP++                      |

| Outputs               | (DP or HDMI)                 |

|                       | 1x USB3.2                    |

| USB De-mux & Re-timer | Yes                          |

| HDCP2.2               | Yes                          |

| HDR, Pixel Processor  | Yes                          |

| DSC & FEC             | Yes                          |

| Package               | LFBGA 12x12mm / 0.65mm pitch |

## **Applications**

The target applications of the KTM5030 are:

- Mobile PC docking stations

- Dongles

- MST video hubs

- AR / VR devices

- High end displays such as digital signage

- Daisy-chain monitors

DisplayPort and USB Type-C are the prominent interfaces in these applications and the KTM5030 offers the highest performance at the optimum bill of material cost.

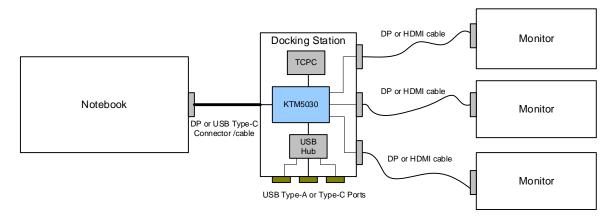

#### **Docking Station Application**

In a mobile docking station topology, the KTM5030 is part of a larger system which has a system controller such as TCPC, USB hub, etc. The docking station can be a traditional dock with a custom connector or a travel dock with a USB Type-C tethered cable. The audio-video interface between the notebook and the docking station is either DP or DP Alt-Mode over USB Type-C. The KTM5030 is an ideal device for a Type-C docking station where it can function as a Type-C Port Manager (TCPM) along with an external TCPC device (e.g. Kinetic MCDP9000 TCPC). It is designed with integrated features such as a USB-C de-mux, a video hub, a protocol converter, and an HDCP repeater in a single chip. The downstream video ports can be configured as DP1.4a or HDMI2.0 depending on the requirements.

Figure 1. KTM5030 Docking Station Use Case

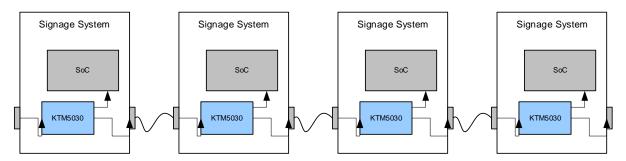

#### **Daisy-Chain Monitor / Signage Application**

A daisy-chain monitor or signage featuring the USB Type-C connector supporting the DP Alt-mode requires a USB Type-C de-mux and a DP MST hub device with two or more video outputs. KTM5030 is an ideal fit for such applications where it can receive the USB and multiple video streams simultaneously. It then routes one of the video stream to the internal SoC and the remaining streams to the downstream units. In this use case, the KTM5030 can support two 4K60Hz displays without DSC or up to four 4K60Hz displays with DSC.

For a Large Format Display Application, such as a 5x5 video wall configuration, KTM5030 can support 25 or more daisy chained displays.

Figure 2. KTM5030 Digital Signage Use Case

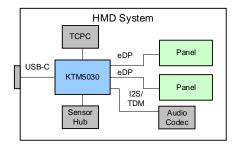

### **AR/VR Application**

The current AR/VR head mount displays use a video splitter device for routing the video from the graphics source to the dual OLED panels. Future designs are targeting higher video resolutions, refresh rates, and low latency. The KTM5030 is suitable for such designs; it can deliver up to 2x 2560x2160 @120 Hz without DSC or up to 2x 3860x2160@ 90 Hz with DSC. Additionally, the KTM5030 can generate a global frame synchronization signal for synchronizing the video with the sensor inputs. Also it can deliver up to 8CH compressed or LPCM audio through the I2S or TDM format to audio codec for the best quality audio experience.

Figure 3, KTM5030 AR/VR Head Mount Display Use Case

## **Functional Block Diagram**

# **BGA Footprints and Pin Mapping**

The ball grid array (BGA) diagrams give the allocation of pins to the package shown, from the top looking down, using the PCB footprint.

Some signal names in BGA diagrams have been abbreviated. Refer to the pin list for full signal names sorted by pin number.

|   | 1                    | 2                    | 3                    | 4                    | 5               | 6                    | 7                    | 8                    | 9                    | 10                   | 11                   | 12              | 13                   | 14                   | 15                   | 16                         | 17                         |   |

|---|----------------------|----------------------|----------------------|----------------------|-----------------|----------------------|----------------------|----------------------|----------------------|----------------------|----------------------|-----------------|----------------------|----------------------|----------------------|----------------------------|----------------------------|---|

| A | HPD_OUT_<br>GPIO2    | GND                  | SSRX2P<br>_RX3N      | GND                  | SSTX2P<br>_RX2N | GND                  | RX_REXT              | REFCLK_OU<br>T       | GND                  | SSTX1P<br>_RX1P      | GND                  | SSRX1P<br>_RX0P | GND                  | TX0_ SSRXP           | GND                  | TX0_SSTXP                  | GND                        | А |

| В | I2CM_SCL_<br>PCONF1  | GND                  | SSRX2N<br>_RX3P      | GND                  | SSTX2N<br>_RX2P | GND                  | EXT_RESETN           | GND                  | GND                  | SSTX1N<br>_RX1N      | GND                  | SSRX1N<br>_RX0N | GND                  | TX0_SSRXN            | GND                  | TX0_ SSTXN                 | GND                        | В |

| С | ALERTN_PP<br>OL      | GND                  | GND                  | GND                  | GND             | GND                  | XTAL_IN              | XTAL_OUT             | GND                  | AVDD18_UFP           | AVDD18_UFP           | AVDD18_UFP      | AVDD18_UFP           | GND                  | GND                  | GND                        | GND                        | С |

| D | I2CM_SDA_<br>PCONF0  | GND                  | RX_AUXN_SB<br>U1     | RX_AUXP_S<br>BU2     | AVDDP9_UFP      | AVDDP9_UFP           | AVDDP9_UFP           | AVDDP9_UF<br>P       | AVDDP9_UF<br>P       | AVDDP9_UFP           | AVDDP9_UFP           | AVDDP9_UFP      | AVDDP9_UFP           | GND                  | NC                   | TX1_<br>CONFIG1_G<br>PIO11 | SPI_DO                     | D |

| E | TX3_<br>DDC_SCL      | GPIO0_<br>I2C_SDA    | GND                  | DVDDP9               | GND             | GND                  | GND                  | GND                  | GND                  | GND                  | GND                  | GND             | GND                  | DVDDP9               | DVDD18               | SPI_CLK                    | SPI_HOLD                   | E |

| F | TX3_<br>HPD_IN       | GPIO1_<br>I2C_SCL    | GND                  | DVDDP9               | GND             | GND                  | GND                  | GND                  | GND                  | GND                  | GND                  | GND             | GND                  | DVDDP9               | DVDD18               | SPI_CSN                    | SPI_DI                     | F |

| G | TX2_<br>DDC_SCL      | TX3_<br>DDC_SDA      | DVDD18               | DVDDP9               | GND             | GND                  | GND                  | GND                  | GND                  | GND                  | GND                  | GND             | GND                  | DVDDP9               | TEST                 | SPI_WPN                    | URX_GPIO8                  | G |

| н | TX1_<br>DDC_SDA      | TX2_<br>DDC_SDA      | DVDD18               | DVDDP9               | GND             | GND                  | GND                  | GND                  | GND                  | GND                  | GND                  | GND             | GND                  | DVDDP9               | DVDD18               | UTX_GPIO9                  | TX2_<br>CONFIG1_G<br>PIO12 | н |

| J | TX1_<br>DDC_SCL      | TX2_<br>HPD_IN       | GND                  | DVDDP9               | GND             | GND                  | GND                  | GND                  | GND                  | GND                  | GND                  | GND             | GND                  | DVDDP9               | DVDD18               | DBUG0_GPI<br>O6            | TX3_<br>CONFIG1_G<br>PIO13 | J |

| ĸ | TX1_CEC_G<br>PIO10   | TX1_<br>HPD_IN       | GND                  | DVDDP9               | GND             | GND                  | GND                  | GND                  | GND                  | GND                  | GND                  | GND             | GND                  | DVDDP9               | DVDD18               | I2S_WCK_G<br>PIO14         | DBUG1_GPI<br>07            | к |

| L | TX3_CEC_G<br>PIO36   | GPIO37_TX2<br>_CEC   | GND                  | DVDDP9               | GND             | GND                  | GND                  | GND                  | GND                  | GND                  | GND                  | GND             | GND                  | DVDDP9               | DVDD18               | I2S_D0_GPI<br>O16          | I2S_FCK_G<br>PIO15         | L |

| м | GND                  | GND                  | TX2_AUX_N            | DVDDP9               | GND             | GND                  | GND                  | GND                  | GND                  | GND                  | GND                  | GND             | GND                  | DVDDP9               | I2S_D2_GPIO<br>18    | I2S_D3_GPI<br>O19          | I2S_D1_GPI<br>017          | м |

| N | TX1_L3_HD<br>MICLK_N | GND                  | TX2_AUX_P            | GND                  | GND             | GND                  | GND                  | GND                  | GND                  | GND                  | GND                  | GND             | GND                  | GND                  | GND                  | GND                        | GND                        | N |

| Р | TX1_L3_HD<br>MICLK_P | GND                  | TX1_AUX_N            | AVDDP9_TX            | AVDDP9_TX       | AVDDP9_TX            | AVDDP9_TX            | AVDDP9_TX            | AVDDP9_TX            | AVDDP9_TX            | AVDDP9_TX            | AVDDP9_TX       | AVDDP9_TX            | GND                  | TX3_AUX_N            | GND                        | TX3_L0_HD<br>MICH2_P       | Р |

| R | TX1_L2_HD<br>MICH0_N | GND                  | TX1_AUX_P            | AVDD18_TX            | TX1_CM          | AVDD18_TX            | AVDD18_TX            | TX2_CM               | AVDD18_TX            | AVDD18_TX            | AVDD18_TX            | TX3_CM          | AVDD18_TX            | GND                  | TX3_AUX_P            | GND                        | TX3_L0_HD<br>MICH2_N       | R |

| т | TX1_L2_HD<br>MICH0_P | GND                  | GND                  | GND                  | GND             | TX2_L3_HDMI<br>CLK_N | GND                  | GND                  | GND                  | GND                  | TX2_L0_HDMI<br>CH2_P | GND             | GND                  | GND                  | GND                  | GND                        | TX3_L1_HD<br>MICH1_P       | т |

| U | TX1_L1_HD<br>MICH1_N | TX1_L1_HD<br>MICH1_P | TX1_L0_HDMI<br>CH2_N | TX1_L0_HD<br>MICH2_P | GND             | TX2_L3_HDMI<br>CLK_P | TX2_L2_HDMI<br>CH0_N | TX2_L2_HDM<br>ICH0_P | TX2_L1_HDM<br>ICH1_N | TX2_L1_HDM<br>ICH1_P | TX2_L0_HDMI<br>CH2_N | GND             | TX3_L3_HDMI<br>CLK_N | TX3_L3_HDMI<br>CLK_P | TX3_L2_HDMI<br>CH0_N | TX3_L2_HD<br>MICH0_P       | TX3_L1_HD<br>MICH1_N       | U |

|   | 1                    | 2                    | 3                    | 4                    | 5               | 6                    | 7                    | 8                    | ,<br>OD \/IE         | 10                   | 11                   | 12              | 13                   | 14                   | 15                   | 16                         | 17                         |   |

**TOP VIEW**

289-Pin 12.0mm x 12.0mm x 1.3mm LFBGA Package, 0.65mm pitch

Figure 4. KTM5030 BGA Diagram

289-Pin 12.0mm x 12.0mm x 1.3mm LFBGA Package, 0.65mm pitch

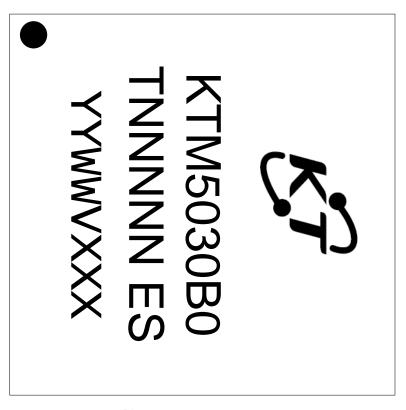

**Table 2. Field Marking Description**

| Field  | Description                                                                                 | Marking      |

|--------|---------------------------------------------------------------------------------------------|--------------|

| DOT    | Pin1 indicator                                                                              | DOT          |

| Line 1 | Company logo                                                                                | Kinetic Logo |

| Line 2 | Part Number + IC revision                                                                   | KTM5030B0    |

| Line 3 | Traceability codes TNNNNN: Fab Lot Number ES: for Engineering Samples                       | "Variant"    |

| Line 4 | YYWW: Assembly Date Code (Work Year & Work Week) V: Assembly Vendor Code XXX: Serial Number | "Variant"    |

Table 3. Pin List

| Table 3. Fill List |                 |  |  |  |  |

|--------------------|-----------------|--|--|--|--|

| Pin#               | Name            |  |  |  |  |

| A1                 | HPD_OUT_GPIO2   |  |  |  |  |

| A2                 | GND             |  |  |  |  |

| А3                 | SSRX2P_RX3N     |  |  |  |  |

| A4                 | GND             |  |  |  |  |

| A5                 | SSTX2P _RX2N    |  |  |  |  |

| A6                 | GND             |  |  |  |  |

| A7                 | RX_REXT         |  |  |  |  |

| A8                 | REFCLK_OUT      |  |  |  |  |

| A9                 | GND             |  |  |  |  |

| A10                | SSTX1P _RX1P    |  |  |  |  |

| A11                | GND             |  |  |  |  |

| A12                | SSRX1P_RX0P     |  |  |  |  |

| A13                | GND             |  |  |  |  |

| A14                | TX0_ SSRXP      |  |  |  |  |

| A15                | GND             |  |  |  |  |

| A16                | TX0_ SSTXP      |  |  |  |  |

| A17                | GND             |  |  |  |  |

| B1                 | I2CM_SCL_PCONF1 |  |  |  |  |

| B2                 | GND             |  |  |  |  |

| В3                 | SSRX2N _RX3P    |  |  |  |  |

| B4                 | GND             |  |  |  |  |

| B5                 | SSTX2N _RX2P    |  |  |  |  |

| В6                 | GND             |  |  |  |  |

| B7                 | EXT_RESETN      |  |  |  |  |

| B8                 | GND             |  |  |  |  |

| В9                 | GND             |  |  |  |  |

| B10                | SSTX1N_RX1N     |  |  |  |  |

| B11                | GND             |  |  |  |  |

| B12                | SSRX1N _RX0N    |  |  |  |  |

| B13                | GND             |  |  |  |  |

| B14                | TX0_ SSRXN      |  |  |  |  |

| B15                | GND             |  |  |  |  |

| B16                | TX0_ SSTXN      |  |  |  |  |

| B17                | GND             |  |  |  |  |

| C1                 | ALERTN_PPOL     |  |  |  |  |

| C2                 | GND             |  |  |  |  |

| C3                 | GND             |  |  |  |  |

| C4                 | GND             |  |  |  |  |

| C5                 | GND             |  |  |  |  |

| C6                 | GND             |  |  |  |  |

| C7                 | XTAL_IN         |  |  |  |  |

| C8                 | XTAL_OUT        |  |  |  |  |

| Pin#       | Name                   |  |  |

|------------|------------------------|--|--|

| C9         | GND                    |  |  |

| C10        | AVDD18_UFP             |  |  |

| C11        | AVDD18_UFP             |  |  |

| C12        | AVDD18_UFP             |  |  |

| C13        | AVDD18_UFP             |  |  |

| C14        | GND                    |  |  |

| C15        | GND                    |  |  |

| C16        | GND                    |  |  |

| C17        | GND                    |  |  |

| D1         | I2CM_SDA_PCONF0        |  |  |

| D2         | GND                    |  |  |

| D3         | RX_AUXN_SBU1           |  |  |

| D4         | RX_AUXP_SBU2           |  |  |

| D5         | AVDDP9_UFP             |  |  |

| D6         | AVDDP9_UFP             |  |  |

| D7         | AVDDP9_UFP             |  |  |

| D8         | AVDDP9_UFP             |  |  |

| D9         | AVDDP9_UFP             |  |  |

| D10        | AVDDP9_UFP             |  |  |

| D11        | AVDDP9_UFP             |  |  |

| D12        | AVDDP9_UFP             |  |  |

| D13        | AVDDP9_UFP             |  |  |

| D14        | GND                    |  |  |

| D15        | NC                     |  |  |

| D16        | TX1_<br>CONFIG1_GPIO11 |  |  |

| D17        | SPI_DO                 |  |  |

| E1         | TX3_DDC_SCL            |  |  |

| E2         | GPIO0_I2C_SDA          |  |  |

| E3         | GND                    |  |  |

| E4         | DVDDP9                 |  |  |

| E5         | GND                    |  |  |

| E6         | GND                    |  |  |

| E7         | GND                    |  |  |

| E8         | GND                    |  |  |

| E9         | GND                    |  |  |

| E10        | GND                    |  |  |

| E11        | GND                    |  |  |

| E12        | GND                    |  |  |

| E13        | GND                    |  |  |

| E14        | DVDDP9                 |  |  |

| E15 DVDD18 |                        |  |  |

| E16        | SPI_CLK                |  |  |

| -          | _ :                    |  |  |

| Pin # | Name          |  |  |

|-------|---------------|--|--|

| E17   | SPI_HOLD      |  |  |

| F1    | TX3_HPD_IN    |  |  |

| F2    | GPIO1_I2C_SCL |  |  |

| F3    | GND           |  |  |

| F4    | DVDDP9        |  |  |

| F5    | GND           |  |  |

| F6    | GND           |  |  |

| F7    | GND           |  |  |

| F8    | GND           |  |  |

| F9    | GND           |  |  |

| F10   | GND           |  |  |

| F11   | GND           |  |  |

| F12   | GND           |  |  |

| F13   | GND           |  |  |

| F14   | DVDDP9        |  |  |

| F15   | DVDD18        |  |  |

| F16   | SPI_CSN       |  |  |

| F17   | SPI_DI        |  |  |

| G1    | TX2_DDC_SCL   |  |  |

| G2    | TX3_DDC_SDA   |  |  |

| G3    | DVDD18        |  |  |

| G4    | DVDDP9        |  |  |

| G5    | GND           |  |  |

| G6    | GND           |  |  |

| G7    | GND           |  |  |

| G8    | GND           |  |  |

| G9    | GND           |  |  |

| G10   | GND           |  |  |

| G11   | GND           |  |  |

| G12   | GND           |  |  |

| G13   | GND           |  |  |

| G14   | DVDDP9        |  |  |

| G15   | TEST          |  |  |

| G16   | SPI_WPN       |  |  |

| G17   | URX_GPIO8     |  |  |

| H1    | TX1_DDC_SDA   |  |  |

| H2    | TX2_DDC_SDA   |  |  |

| H3    | DVDD18        |  |  |

| H4    | DVDDP9        |  |  |

| H5    | GND           |  |  |

| H6    | GND           |  |  |

| H7    | GND           |  |  |

|       |               |  |  |

GND Continues on page 12

## Pint List (Continued)

| Pin#       | Name                   |  |

|------------|------------------------|--|

| H8         | GND                    |  |

| H9         | GND                    |  |

| H10        | GND                    |  |

| H11        | GND                    |  |

| H12        | GND                    |  |

| H13        | GND                    |  |

| H14        | DVDDP9                 |  |

| H15        | DVDD18                 |  |

| H16        | UTX_GPIO9              |  |

| H17        | TX2_<br>CONFIG1_GPIO12 |  |

| J1         | TX1_DDC_SCL            |  |

| J2         | TX2_HPD_IN             |  |

| J3         | GND                    |  |

| J4         | DVDDP9                 |  |

| J5         | GND                    |  |

| J6         | GND                    |  |

| J7         | GND                    |  |

| J8         | GND                    |  |

| J9         | GND                    |  |

| J10        | GND                    |  |

| J11        | GND                    |  |

| J12        | GND                    |  |

| J13        | GND                    |  |

| J14        | DVDDP9                 |  |

| J15        | DVDD18                 |  |

| J16        | DBUG0_GPIO6            |  |

| J17        | TX3_<br>CONFIG1_GPIO13 |  |

| K1         | TX1_CEC_GPIO10         |  |

| K2         | TX1_HPD_IN             |  |

| K3         | GND                    |  |

| K4         | DVDDP9                 |  |

| K5         | GND                    |  |

| K6         | GND                    |  |

| K7         | GND                    |  |

| K8         | GND                    |  |

| K9         | GND                    |  |

| K10        | GND                    |  |

| K11        | GND                    |  |

| K12        | GND                    |  |

| K13        | GND                    |  |

| K14        | DVDDP9                 |  |

| K15 DVDD18 |                        |  |

| Name                |  |  |

|---------------------|--|--|

| I2S_WCK_GPIO14      |  |  |

| DBUG1_GPIO7         |  |  |

| TX3_CEC_GPIO36      |  |  |

| GPIO37_TX2_CEC      |  |  |

| GND                 |  |  |

| DVDDP9              |  |  |

| GND                 |  |  |

| DVDDP9              |  |  |

| DVDD18              |  |  |

| I2S_D0_GPIO16       |  |  |

| I2S_FCK_GPIO15      |  |  |

| GND                 |  |  |

| GND                 |  |  |

| TX2_AUX_N           |  |  |

| DVDDP9              |  |  |

| GND                 |  |  |

| DVDDP9              |  |  |

| I2S_D2_GPIO18       |  |  |

| I2S_D3_GPIO19       |  |  |

| I2S_D1_GPIO17       |  |  |

| N1 TX1_L3_HDMICLK_N |  |  |

| N2 GND              |  |  |

| N3 TX2_AUX_P        |  |  |

| GND                 |  |  |

| GND                 |  |  |

| GND                 |  |  |

|                     |  |  |

| Name             |  |  |  |

|------------------|--|--|--|

| GND              |  |  |  |

| TX1_L3_HDMICLK_P |  |  |  |

| GND              |  |  |  |

| TX1_AUX_N        |  |  |  |

| AVDDP9_TX        |  |  |  |

| GND              |  |  |  |

| TX3_AUX_N        |  |  |  |

| GND              |  |  |  |

| TX3_L0_HDMICH2_P |  |  |  |

| TX1_L2_HDMICH0_N |  |  |  |

| GND              |  |  |  |

| TX1_AUX_P        |  |  |  |

| AVDD18_TX        |  |  |  |

| TX1_CM           |  |  |  |

| AVDD18_TX        |  |  |  |

| AVDD18_TX        |  |  |  |

| TX2_CM           |  |  |  |

| AVDD18_TX        |  |  |  |

| AVDD18_TX        |  |  |  |

| AVDD18_TX        |  |  |  |

| TX3_CM           |  |  |  |

| AVDD18_TX        |  |  |  |

| GND              |  |  |  |

|                  |  |  |  |

Continues on page 13

## Pint List (Continued)

| Pin # | Name             |  |  |  |

|-------|------------------|--|--|--|

| R15   | TX3_AUX_P        |  |  |  |

| R16   | GND              |  |  |  |

| R17   | TX3_L0_HDMICH2_N |  |  |  |

| T1    | TX1_L2_HDMICH0_P |  |  |  |

| T2    | GND              |  |  |  |

| T3    | GND              |  |  |  |

| T4    | GND              |  |  |  |

| T5    | GND              |  |  |  |

| T6    | TX2_L3_HDMICLK_N |  |  |  |

| T7    | GND              |  |  |  |

| T8    | GND              |  |  |  |

| Т9    | GND              |  |  |  |

| T10   | GND              |  |  |  |

| T11   | TX2_L0_HDMICH2_P |  |  |  |

| T12   | GND              |  |  |  |

| T13   | GND              |  |  |  |

| T14   | GND              |  |  |  |

| T15   | GND              |  |  |  |

| T16   | GND              |  |  |  |

| T17   | TX3_L1_HDMICH1_P |  |  |  |

| U1    | TX1_L1_HDMICH1_N |  |  |  |

| U2    | TX1_L1_HDMICH1_P |  |  |  |

| U3    | TX1_L0_HDMICH2_N |  |  |  |

| U4    | TX1_L0_HDMICH2_P |  |  |  |

| U5    | GND              |  |  |  |

| U6    | TX2_L3_HDMICLK_P |  |  |  |

| U7    | TX2_L2_HDMICH0_N |  |  |  |

| U8    | TX2_L2_HDMICH0_P |  |  |  |

| U9    | TX2_L1_HDMICH1_N |  |  |  |

| U10   | TX2_L1_HDMICH1_P |  |  |  |

| U11   | TX2_L0_HDMICH2_N |  |  |  |

| U12   | GND              |  |  |  |

| U13   | TX3_L3_HDMICLK_N |  |  |  |

| U14   | TX3_L3_HDMICLK_P |  |  |  |

| U15   | TX3_L2_HDMICH0_N |  |  |  |

| U16   | TX3_L2_HDMICH0_P |  |  |  |

| U17   | TX3_L1_HDMICH1_N |  |  |  |

## **Ordering Information**

| Part Number | Functional Description                          | Marking <sup>1</sup> | Operating<br>Temperature | Package    | External<br>Package |

|-------------|-------------------------------------------------|----------------------|--------------------------|------------|---------------------|

| KTM5030B0   | USB-C/ DP alt-mode                              |                      |                          |            | TRAYS               |

| KTM5030B0T  | DP 4 lanes OR 2 lanes DP and 2 lanes USB3.2 DSC | KTM5030B0            | 0°C to +70°C             | 289- LFBGA | Tape and Reel       |

# **Absolute Maximum Ratings<sup>2</sup>**

(T<sub>A</sub> = 25°C unless otherwise noted)

| Symbol                | Description                                            | Value        | Units |

|-----------------------|--------------------------------------------------------|--------------|-------|

| V <sub>VDD_1.8</sub>  | VDD1.8V to GND                                         | -0.3 to 2.16 | V     |

| V <sub>VDD_0.95</sub> | VIO0.95V to GND                                        | -0.3 to 1.14 | V     |

| V <sub>IN5tol</sub>   | Input voltage tolerance for 3.3V, 5V tolerant I/O pins | -0.3 to 5.5  | V     |

| Tstg                  | Storage temperature                                    | -40 to 150   | °C    |

| Tsol                  | Peak IR reflow soldering temperature                   | 260          | °C    |

# ESD and Latch-up Ratings<sup>3</sup>

| Symbol                | Description                          | Value | Units |

|-----------------------|--------------------------------------|-------|-------|

| V <sub>ESD_</sub> HBM | JEDEC JESD22-A114 ESD HBM (all pins) | ±2.0  | kV    |

| Vesd_cdm              | JEDEC JESD22-C101 ESD CDM (all pins) | ±500  | V     |

| ILU                   | JEDEC JESD78                         | ±100  | mA    |

# Thermal Capabilities<sup>4</sup>

| Symbol | Description                              | Value    | Units |

|--------|------------------------------------------|----------|-------|

| Оја    | Thermal Resistance – Junction to Ambient | 27       | °C/W  |

| Олс    | Thermal Resistance – Junction to Case    | 8.473    | °C/W  |

| TA     | Ambient Operating Temperature Range      | 0 to 70  | °C    |

| TJ     | Junction Operating Temperature Range     | 0 to 125 | °C    |

March 2023 - Revision 04d Page 12 of 35

<sup>1.</sup> See Table 1 for trace codes marking details;. ES - Engineering Sample.

<sup>2.</sup> Stresses above those listed in Absolute Maximum Ratings may cause permanent damage to the device. Functional operation at conditions other than the operating conditions specified is not implied. Only one Absolute Maximum rating should be applied at any one time.

<sup>3.</sup> ESD and Latch-up Ratings conform to JEDEC industry standards. Some pins may actually have higher performance. Ratings apply with chip enabled, disabled, or unpowered, unless otherwise noted.

<sup>4.</sup> Junction to Ambient thermal resistance is highly dependent on PCB layout. Values are based on thermal properties of the device when soldered to a four-layer JEDEC PCB board, no heat spreader, and no air flow.

## Electrical Characteristics<sup>5</sup>

Unless otherwise noted, the *Min* and *Max* specs are applied over the full operation temperature range of  $0^{\circ}$ C to +70°C and  $V_{DD\_1.8V} = 1.8V$ ,  $V_{DD\_0.95V} = 0.95V$ . Typical values are specified at  $T_A = +25^{\circ}$ C.

# **DC Characteristics**

**Supply Specifications**

| Symbol                 | Description                                                                                                                                                     | Conditions                                                                                                          | Min  | Тур              | Max  | Units |

|------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------|------|------------------|------|-------|

| V <sub>VDD_1.8</sub>   | 1.8V supply voltages (analog and digital)                                                                                                                       |                                                                                                                     | 1.71 | 1.8              | 1.89 | V     |

| V <sub>VDD_0.9</sub>   | 0.95V supply voltages (analog and digital)                                                                                                                      |                                                                                                                     | 0.90 | 0.95             | 1.00 | V     |

| Power                  |                                                                                                                                                                 |                                                                                                                     |      |                  |      |       |

|                        | Protocol converter Mode<br>Measurement condition:<br>Nominal corner, 25°C, Nominal power supply                                                                 |                                                                                                                     |      |                  |      |       |

|                        | Operating condition 1<br>Input: DP MST HBR3 (4L)<br>Output1: DP SST HBR3 (4L) 4k2k30Hz<br>Output2: DP SST HBR3 (4L) 4k2k30Hz<br>Output3: HDMI 4k2k30Hz          |                                                                                                                     |      | 550              | 600  | mW    |

|                        | Operating condition 2<br>Input: DP MST HBR3 (4L)<br>Output1: DP SST HBR3 (4L) 1080p60Hz<br>Output2: DP SST HBR3 (4L) 4k2k30Hz<br>Output3: HDMI 4k2k60Hz         |                                                                                                                     |      | 626              | 711  | mW    |

|                        | Operating condition 3<br>Input: DP SST HBR3 (4L) 4k2k60Hz<br>Output1: DP SST HBR3 (4L) 4k2k60Hz<br>Output2: DP SST HBR3 (4L) 4k2k60Hz<br>Output3: HDMI 4k2k60Hz |                                                                                                                     |      | 712              | 795  | mW    |

|                        | Standby                                                                                                                                                         |                                                                                                                     |      | 9.2              |      | mW    |

| I <sub>DD_0.95</sub> V | 0.95V Supply Current                                                                                                                                            | Nominal corner, 25°C,                                                                                               |      | 733 <sup>6</sup> | 892  | mA    |

| I <sub>DD_1.8V</sub>   | 1.8V Supply Current <sup>7</sup>                                                                                                                                | Nominal power supply Operating condition 3 (See above) VDD (analog and digital) 0.95V VDD (analog and digital) 1.8V |      | 146              | 155  | mA    |

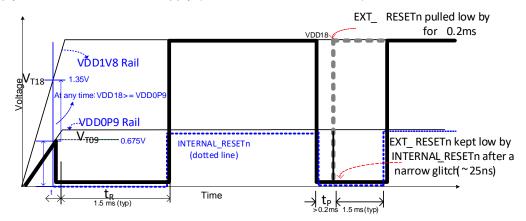

| T <sub>RAMP_MIN</sub>  | Minimum Power Rail Ramp up Time                                                                                                                                 |                                                                                                                     | 100  |                  |      | μS    |

March 2023 - Revision 04d

<sup>5.</sup> Device is guaranteed to meet performance specifications over the 0°C to +70°C operating temperature range by design, characterization and correlation with statistical process controls.

<sup>6.</sup> Values are for Power Supply design only and not indicative for Max Power Consumption.

<sup>7.</sup> Ripple amplitude for power supplies should be 20mV or lower with max ripple frequency up to 30MHz.

Unless otherwise noted, the *Min* and *Max* specs are applied over the full operation temperature range of  $0^{\circ}\text{C}$  to  $+70^{\circ}\text{C}$  and  $V_{DD\_1.8V} = 1.8V$ ,  $V_{DD\_0.95V} = 0.95V$ . Typical values are specified at  $T_A = +25^{\circ}\text{C}$ .

3.3V IO Signals, 5V Tolerant Open Drain Type

| Symbol              | Description                                             | Conditions | Min | Тур | Max  | Units |

|---------------------|---------------------------------------------------------|------------|-----|-----|------|-------|

| $V_{PAD}$           | Input Voltage at PAD                                    |            |     | 5   | 6    | V     |

| V <sub>IH</sub>     | Input High voltage                                      |            | 2.0 |     |      | V     |

| VIL                 | Input Low voltage                                       |            |     |     | 0.8  | V     |

| VoL                 | Output Low voltage                                      |            |     |     | 0.4  | V     |

| loL                 | Output Low current (measured at V <sub>OL</sub> = 0.4V) |            | 5.3 | 8.7 | 10.7 | mA    |

| I <sub>IL</sub>     | Input Leakage current                                   |            |     | 2.4 | 3.8  | μА    |

| I <sub>IL_off</sub> | Input Leakage in Fail Safe (unpowered VDD/VREF)         |            |     | 2   | 3.2  | μΑ    |

| I <sub>vref</sub>   | VREF DC current                                         |            |     | 0.1 | 0.8  | nA    |

| $I_{vdd}$           | VDD DC current                                          |            |     | 0.8 | 3.9  | μΑ    |

1.8V IO Signals, 1.8V Tolerant, TRISTATE

| Symbol          | Description                      | Conditions | Min  | Тур | Max  | Units |

|-----------------|----------------------------------|------------|------|-----|------|-------|

| VIH             | Input High voltage               |            | 1.25 |     |      | V     |

| V <sub>IL</sub> | Input Low voltage                |            |      |     | 0.55 | V     |

| Vol             | Output Low voltage               |            |      |     | 0.45 | V     |

| Vон             | Output High voltage              |            | 1.35 |     |      | V     |

| Іін             | Input Lookage current            |            | -10  |     | 10   | μА    |

| I⊫              | Input Leakage current            |            | -10  |     | 10   | μΑ    |

| loz             | Tri-state output Leakage current |            | -10  |     | 10   | μА    |

| R <sub>PU</sub> | Pull-up Resistor                 |            |      | 80  |      | kΩ    |

| $R_{PD}$        | Pull-down Resistor               |            |      | 95  |      | kΩ    |

Unless otherwise noted, the *Min* and *Max* specs are applied over the full operation temperature range of  $0^{\circ}$ C to +70°C and  $V_{DD\_1.8V} = 1.8V$ ,  $V_{DD\_0.95V} = 0.95V$ . Typical values are specified at  $T_A = +25^{\circ}$ C.

## **AC Characteristics<sup>8</sup>**

**Maximum Speed of Operation**

| Symbol           | Description                   | Conditions | Min | Тур | Max | Units |

|------------------|-------------------------------|------------|-----|-----|-----|-------|

| T <sub>CLK</sub> | Reference Input Clock         |            |     |     | 25  | MHz   |

| Oclk             | On-Chip Microcontroller Clock |            |     |     | 300 | MHz   |

| SLAVE_scl        | I2C host interface clock      |            |     |     | 400 | kHz   |

| MSTRx_scl        | DDC Master                    |            |     |     | 400 | kHz   |

| SPI              | SPI Clock                     |            |     |     | 75  | MHz   |

## **DisplayPort Receiver Characteristics**

**Receiver Operating Range**

| Symbol                       | Description                      | Conditions | Min | Тур | Max | Units |

|------------------------------|----------------------------------|------------|-----|-----|-----|-------|

| V <sub>RX_DIF_PP_RANGE</sub> | Differential Input Voltage Range |            | 40  |     | 800 | mV    |

| R <sub>RX_TERM_RANGE</sub>   | RX Termination Control Range     |            | 80  | 100 | 120 | Ω     |

**System Parameters**

| Symbol             | Description                  | Conditions                                   | Min | Тур | Max | Units |

|--------------------|------------------------------|----------------------------------------------|-----|-----|-----|-------|

| UI <sub>HBR3</sub> | HBR3 unit interval (8.1Gbps) |                                              |     | 123 |     | Ps    |

| UI <sub>HBR2</sub> | HBR2 unit interval (5.4Gbps) |                                              |     | 185 |     | Ps    |

| UI <sub>HBR</sub>  | HBR unit interval (2.7Gbps)  |                                              |     | 370 |     | Ps    |

| UI <sub>RBR</sub>  | RBR unit interval (1.62Gbps) |                                              |     | 617 |     | ps    |

|                    | Link clock down spreading    | Modulation frequency range of 30kHz to 33kHz | 0   |     | 0.5 | %     |

March 2023 - Revision 04d Page 15 of 35 Kinetic Technologies Confidential

<sup>8.</sup> AC characteristics parameters are guaranteed by the silicon characterization across operating condition unless otherwise specified. Not all parameters are tested in the production test.

Unless otherwise noted, the Min and Max specs are applied over the full operation temperature range of 0°C to +70°C and  $V_{DD\_1.8V} = 1.8V$ ,  $V_{DD\_0.95V} = 0.95V$ . Typical values are specified at  $T_A = +25$ °C.

### **Main Link and AUX CH Parameters**

| Symbol                       | Description                                    | Conditions         | Min  | Тур | Max   | Units |

|------------------------------|------------------------------------------------|--------------------|------|-----|-------|-------|

| Main Link Jitter Tol         | erance, Target Bit Error Rate 10 <sup>-9</sup> |                    |      |     |       |       |

| T <sub>RX_TJ_RBR</sub>       | RBR Total jitter at TP3                        | EH = 56 mVdiff_pp  |      |     | 0.747 | UI    |

| T <sub>RX_Non-ISI_RBR</sub>  | RBR non-ISI jitter                             |                    |      |     | 0.177 | UI    |

| T <sub>RX_TJ_HBR</sub>       | HBR Total jitter at TP3_EQ                     | EH = 160 mVdiff_pp |      |     | 0.491 | UI    |

| T <sub>RX_Non-ISI_HBR</sub>  | HBR non-ISI jitter                             |                    |      |     | 0.330 | UI    |

| T <sub>RX_TJ_HBR2</sub>      | HBR2 Total jitter at TP3_EQ                    | EH = 100 mVdiff_pp |      |     | 0.62  | UI    |

| T <sub>RX_Non-ISI_HBR2</sub> | HBR2 non-ISI jitter                            |                    |      |     | 0.40  | UI    |

| T <sub>RX_TJ_HBR3</sub>      | HBR3 Total jitter at TP3_CTLE                  | EH = 50 mVdiff_pp  |      |     | 0.62  | UI    |

| T <sub>RX_NON_ISI_HBR3</sub> | HBR3 non-ISI jitter                            |                    |      |     | 0.38  | UI    |

| AUX Parameters               |                                                |                    |      |     |       |       |

| Vaux_rx_dif_range            | Differential Input Voltage Range               | TP3                | 0.27 |     | 1.36  | V     |

| Vaux_tx_dif_range            | Differential Output Voltage<br>Range           |                    | 0.29 |     | 1.38  | V     |

| RAUX_TERM_RANGE              | RX DIFF Termination Control Range              |                    |      | 100 |       | Ω     |

Unless otherwise noted, the *Min* and *Max* specs are applied over the full operation temperature range of  $0^{\circ}$ C to +70°C and  $V_{DD\_1.8V} = 1.8V$ ,  $V_{DD\_0.95V} = 0.95V$ . Typical values are specified at  $T_A = +25^{\circ}$ C.

# **DisplayPort Transmitter Characteristics**

**Transmitter Operating Range**

| Symbol                             | Description                       | Conditions                                                         | Min  | Тур | Max  | Units  |

|------------------------------------|-----------------------------------|--------------------------------------------------------------------|------|-----|------|--------|

| V <sub>TX_DIF_PP_RANGE</sub>       | Differential Output Voltage Range |                                                                    |      |     | 1.38 | V      |

| RTX_TERM_RANGE                     | TX Termination Control Range      |                                                                    | 80   | 100 | 120  | Ω      |

| DisplayPort Transmit               | ter System Parameters             |                                                                    |      |     |      |        |

| UI <sub>HBR3</sub>                 | HBR3 unit interval (8.1Gbps)      |                                                                    |      | 123 |      | ps     |

| UI <sub>HBR2</sub>                 | HBR2 unit interval (5.4Gbps)      |                                                                    |      | 185 |      | ps     |

| UI <sub>RBR</sub>                  | HBR unit interval (2.7Gbps)       |                                                                    |      | 370 |      | ps     |

| $UI_RBR$                           | RBR unit interval (1.62Gbps)      |                                                                    |      | 617 |      | ps     |

|                                    | Link clock down spreading         | Modulation frequency range of 30kHz to 33kHz                       | 0    |     | 0.5  | %      |

| $C_{TX}$                           | Coupling capacitor                | All Main lanes and AUX CH need AC coupling on the transmitter side |      | 100 |      | nF     |

| DisplayPort Transmit               | ter TP2 Parameters                |                                                                    |      |     |      |        |

| T <sub>TX_SKEW_INTER_PAIR</sub>    | Lane-to-Lane output Skew          | Applies to all pairwise combinations of supported lanes            |      |     | 1250 | ps     |

| TTX_SKEW_INRA_PAIR                 | Lane Intra pair Skew              | Applies to all supported lanes                                     |      |     | 30   | ps     |

| Target bit error rate 1            | 0-9                               |                                                                    |      |     |      |        |

| T <sub>TX_TJ_TPS4_HBR3</sub>       | HBR3 Total Jitter at TP3_CTLE     | VSL/PEL = 1/1, A <sub>dc</sub> = -3 dB                             |      |     | 0.47 | UI     |

| T <sub>TX_NonISI_TPS4_HBR3</sub>   | HBR3 Non-ISI Jitter               |                                                                    |      |     | 0.23 | UI     |

| T <sub>TX_TJ_CP2520_HBR2</sub>     | HBR2 Total Jitter at TP3_EQ       | VSL/PEL = 1/1                                                      |      |     | 0.58 | UI     |

| T <sub>TX_NonISI_CP2520_HBR2</sub> | HBR2 Non-ISI Jitter               |                                                                    |      |     | 0.36 | UI     |

| T <sub>TX_TJ_D10.2_HBR2</sub>      | HBR2 Total Jitter with D10.2      | Measured at TP3_EQ                                                 |      |     | 0.40 | UI     |

| T <sub>TX_DJ_D10.2_HBR2</sub>      | HBR2 Dual-Dirac Jitter with D10.2 | Measured at TP3_EQ                                                 |      |     | 0.27 | UI     |

| T <sub>TX_RJ_D10.2_HBR2</sub>      | HBR2 Random Jitter with D10.2     | Measured at TP3_EQ                                                 |      |     | 19.2 | mUIrms |

| AUX Parameters                     |                                   |                                                                    |      |     |      |        |

| Vaux_rx_diff_pp                    | Differential Input Voltage Range  |                                                                    | 0.27 |     | 1.38 | V      |

| Vaux_tx_diff_pp                    | Differential Output Voltage Range | 50mV/step in 4 steps                                               | 0.29 |     | 1.38 | V      |

| RAUX_TERM_RANGE                    | RX DIFF Termination Control Range |                                                                    |      | 100 |      | Ω      |

Unless otherwise noted, the *Min* and *Max* specs are applied over the full operation temperature range of  $0^{\circ}$ C to +70°C and  $V_{DD\_1.8V} = 1.8V$ ,  $V_{DD\_0.95V} = 0.95V$ . Typical values are specified at  $T_A = +25^{\circ}$ C.

## **HDMI Transmitter I/O Characteristics**

#### **HDMI Transmitter DC Specifications**

| Symbol               | Description                                         | Conditions                                             | Min | Тур | Max | Units |

|----------------------|-----------------------------------------------------|--------------------------------------------------------|-----|-----|-----|-------|

| V <sub>TX_PP</sub>   | Differential output: single ended swing amplitude   |                                                        | 0.4 | 0.5 | 0.6 | V     |

| V <sub>TX_DIF_</sub> | Differential output: Single ended high-level output | Sink supply dependent (typical V <sub>DD</sub> = 3.3V) |     | 3.3 |     | V     |

### **HDMI Transmitter AC Specifications**

| Symbol                         | Description                               | Conditions                                                             | Min | Тур | Max  | Units |

|--------------------------------|-------------------------------------------|------------------------------------------------------------------------|-----|-----|------|-------|

| ftx_chr_clk                    | TMDS Character Clock                      | Programmable                                                           | 25  |     | 600  | MHz   |

| V <sub>TX_DIF_PP</sub>         | Differential Output Voltage               | In 64 steps (usable range 0.8 – 1.2 V)                                 | 0   |     | 1.2  | V     |

| Аркемрн                        | TX Pre-Emphasis Level                     | V <sub>TX_DIF_PP</sub> + A <sub>PREMPH</sub> should be less than 1.2 V | 0   |     | 6    | dB    |

| R <sub>TX_TERM_</sub><br>RANGE | TX Differential Termination Control Range | Programmable Termination (range 85-600)                                |     | 100 |      | Ω     |

| T <sub>TX_CLK_</sub> JITTER    | TX Clock jitter                           | Tighter than HDMI specification                                        |     |     | 0.25 | TBIT  |

|                                | TX Data Jitter                            | Refer to the tables below.                                             |     |     |      |       |

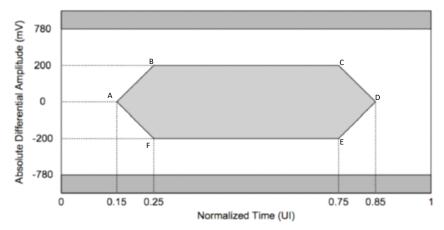

Figure 5. HDMI1.4b EYE Diagram at TP1 at TMDS Character Clock Rate ≤ 340MHz

Table 4. TMDS TX EYE Opening Specification for TMDS Character Clock Rate ≤ 340MHz

| Point | H(UI) | V (mV_diff_pp) |  |

|-------|-------|----------------|--|

| Α     | 0.13  | 0              |  |

| В     | 0.20  | 200            |  |

| С     | 0.80  | 200            |  |

| D     | 0.87  | 0              |  |

| E     | 0.80  | -200           |  |

| F     | 0.20  | -200           |  |

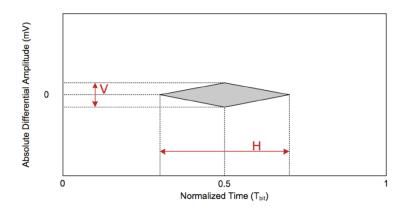

Figure 6. HDMI2.0 EYE Diagram at TP2\_EQ at TMDS Character Clock Rate > 340MHz

Table 5. TMDS TX PHY Jitter Specification at TMDS Character Clock Rate > 340 MHz

| TMDS Bit Rate (Gbps) | H (Tbit)                                            | V (mV_diff_pp)                                     |

|----------------------|-----------------------------------------------------|----------------------------------------------------|

| 3.4 < Rbit < 3.712   | 0.72                                                | 335                                                |

| 3.712 < Rbit ≤ 5.94  | -0.0332 Rbit <sup>2</sup> + 0.2312<br>Rbit + 0.1998 | -19.66 Rbit <sup>2</sup> + 106.74<br>Rbit + 209.58 |

| 5.94 < Rbit ≤ 6.0    | 0.48                                                | 150                                                |

## **USB 3.2x1 Transmitter and Receiver Characteristics**

USB 3.2 x1 transmitter (SSRX pin and Type-C interface in USB mode)

|                                  | , -                                              | ype-C interface in USB mode) | 1      |     |        |            |

|----------------------------------|--------------------------------------------------|------------------------------|--------|-----|--------|------------|

| Symbol                           | Description                                      | Conditions                   | Min    | Тур | Max    | Units      |

| UI <sub>USB_GEN1</sub>           | Unit interval in Gen1                            |                              | 199.94 |     | 200.46 | ps         |

| UI <sub>USB_GEN2</sub>           | Unit interval in Gen2                            |                              | 99.97  |     | 100.03 | ps         |

| C <sub>TX_USB</sub>              | AC coupling capacitor                            |                              | 75     |     | 265    | nF         |

| tssc_freq_<br>DEVIATION          | SSC deviation                                    |                              | 0      |     | -5000  | ppm        |

| tssc_mod_<br>RATE                | Modulation rate                                  |                              | 30     |     | 33     | kHz        |

| Vusb_tx_<br>diff_pp              | Differential peak-to-peak voltage swing          |                              | 0.8    |     | 1.2    | V          |

| VTX_DE_RATIO<br>_GEN1            | De-emphasis in Gen1                              |                              | 3.0    |     | 4.0    | dB         |

| V <sub>TX_PS_RATIO</sub>         | Pre-shoot in Gen2                                |                              | 1.2    |     | 3.2    | dB         |

| VTX_DE_RATIO<br>_GEN2            | De-emphasis in Gen2                              |                              | 2.1    |     | 4.1    | dB         |

| R <sub>TX_DIFF_DC</sub>          | DC differential impedance                        |                              | 72     |     | 120    | Ω          |

| V <sub>TX_RCV_</sub>             | The amount of voltage change during Rx detection |                              |        |     | 0.6    | V          |

| tcdr_slew_<br>RATE               | Maximum slew rate                                | In Gen1                      |        |     | 10     | ms/s       |

| SSC <sub>dfdt</sub>              | SSC df/dt                                        | In Gen2                      |        |     | 1250   | ppm/<br>µs |

| Veye_height_<br>gen1             | Eye height at TP4 in Gen1                        |                              | 100    |     | 1000   | mV         |

| V <sub>EYE_HEIGHT_</sub><br>GEN2 | Eye height at TP4 in Gen2                        |                              | 70     |     | 1000   | mV         |

| Djusb_gen1                       | Deterministic jitter at TP4 in Gen1              |                              |        |     | 430    | mUI        |

| Djusb_gen2                       | Deterministic jitter at TP4 in Gen2              |                              |        |     | 530    | mUI        |

| Rjusb_gen1                       | RMS Random jitter at TP4 in Gen1                 |                              |        |     | 3.22   | ps         |

| Djusb_gen2                       | RMS Deterministic jitter at TP4 in Gen2          |                              |        |     | 1      | ps         |

| Tjusb_gen1                       | Total jitter at TP4 in Gen1                      |                              |        |     | 660    | mUI        |

| Tjusb_gen1                       | Total jitter at TP4 in Gen2                      |                              |        |     | 671    | mUI        |

| t <sub>PERIOD</sub>              | LFPS t <sub>PERIOD</sub>                         |                              | 20     |     | 80     | ns         |

| VTX_DIFF_PP_<br>LFPS             | LFPS peak-to-peak differential amplitude         |                              | 800    |     | 1000   | mV         |

| T <sub>DUTY_LFPS</sub>           | LFPS duty cycle                                  |                              | 40     |     | 60     | %          |

USB 3.2 x1 Receiver (SSRX pin and Type-C interface in USB mode)

| obboth to the transfer and type of montage in obb mode, |                                   |            |        |     |        |       |

|---------------------------------------------------------|-----------------------------------|------------|--------|-----|--------|-------|

| Symbol                                                  | Description                       | Conditions | Min    | Тур | Max    | Units |

| UI <sub>USB_GEN1</sub>                                  | Unit interval in Gen1             |            | 199.94 |     | 200.46 | ps    |

| UI <sub>USB_GEN2</sub>                                  | Unit interval in Gen2             |            | 99.97  |     | 100.23 | ps    |

| tssc_freq_<br>DEVIATION                                 | SSC deviation                     |            | 0      |     | -5000  | ppm   |

| tssc_mod_<br>RATE                                       | Modulation rate                   |            | 30     |     | 33     | kHz   |

| R <sub>RX_DC</sub>                                      | Receiver DC common mode impedance |            | 18     |     | 30     | Ω     |

| R <sub>RX_DIFF_DC</sub>                                 | DC differential impedance         |            | 72     |     | 120    | Ω     |

| ZRX_HIGH_IMP<br>_DC_POS                                 | Receiver high impedance           |            | 10k    |     |        | Ω     |

| VRX_LFPS_<br>DET_DIFFp-p                                | LFPS detect threshold             |            | 100    |     | 300    | mV    |

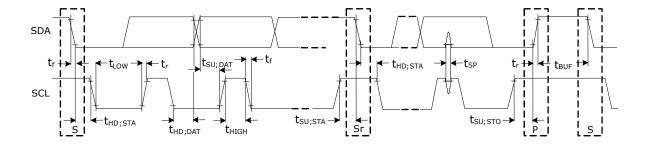

# **DDC (I2C) Interface Timing Characteristics**

**DDC (I2C) Interface Timing**

| Symbol              | Description                          | Conditions                              | Min         | Тур | Max       | Units |

|---------------------|--------------------------------------|-----------------------------------------|-------------|-----|-----------|-------|

| fscL                | SCL clock rate                       | Fast mode                               | 0           | -   | 400       | kHz   |

| t <sub>HD-STA</sub> | Hold time START                      | After this period, the 1st clock starts | 1.2         | -   | -         | μS    |

| $t_{LOW}$           | Low period of clock                  | SCL                                     | 1.3         | -   | -         | μS    |

| t <sub>HIGH</sub>   | High period of clock                 | SCL                                     | 1.2         | 1   | -         | μS    |

| t <sub>su;STA</sub> | Set up time for a repeated START     |                                         | 1.2         | ı   | -         | μS    |

| thd;dat             | Data hold time                       | For master                              | 0.7         | -   | $0.9^{9}$ | μS    |

| t <sub>SU;DAT</sub> | Data setup time                      |                                         | 380         | -   | -         | ns    |

| $T_BUF$             | Bus free time between STOP and START |                                         | 1.3         | 1   | -         | μS    |

| Св                  | Capacitance load for each bus line   |                                         | -           | 100 | 400       | pF    |

| t <sub>r</sub>      | Rise time                            |                                         | 220         | 1   | 300       | ns    |

| t <sub>f</sub>      | Fall time                            |                                         | 60          | -   | 300       | ns    |

| $V_{nh}$            | Noise margin at high level           |                                         | 0.25<br>VDD | 1   | -         | V     |

| $V_{nl}$            | Noise margin at low level            |                                         | 0.2<br>VDD  | -   | -         | V     |

March 2023 - Revision 04d Page 21 of 35 Kinetic Technologies Confidential

<sup>9.</sup> The maximum  $t_{HD;DAT}$  only has to be met if the device does not stretch the low period  $t_{LOW}$  of the SCL signal. In the diagram below, S = start, P = stop, Sr = Repeated start, and SP = Repeated stop conditions.

I2C Host Interface Timing (Figure 7. I2C Timing)

| Symbol                            | Description                                      | Min                           | Тур | Max         | Units |

|-----------------------------------|--------------------------------------------------|-------------------------------|-----|-------------|-------|

| F <sub>SCL</sub>                  | SCL Clock Frequency                              |                               |     | 400         | kHz   |

| thd: DAT                          | Data hold time                                   | 0                             |     | -           | μs    |

| tsu :DAT                          | Data set-up time                                 | 50                            |     | -           | ns    |

| t <sub>R</sub>                    | Rise time of both SDA and SCL signals            | -                             |     | 120         | ns    |

| t <sub>F</sub>                    | Fall time of both SDA and SCL signals            | 20x<br>(V <sub>DD</sub> /5.5) |     | 120         | ns    |

| t <sub>BUF</sub>                  | Bus free time between a STOP and START condition | 0.5                           |     | -           | μs    |

| Св                                | Capacitance load for each bus line               | -                             |     | 550         | pF    |

| t <sub>VD: DAT</sub>              | Data valid time                                  | -                             |     | 0.45        | μs    |

| tvd: ACK                          | Data valid acknowledge time                      | -                             |     | 0.45        | μs    |

| t <sub>I2C_SBR</sub><br>(400 kHz) | Time for I2C SINGLE BYTE READ                    | -                             |     | 110         | μs    |

| t <sub>l2C_SBW</sub><br>(400 kHz) | Time for I2C SINGLE BYTE WRITE                   | -                             |     | 85          | μs    |

| t <sub>I2C_MBR</sub><br>(400 kHz) | Time for I2C Multi BYTE READ                     | -                             |     | 100+35/byte | μs    |

| t <sub>I2C_мвw</sub><br>(400 kHz) | Time for I2C Multi BYTE WRITE                    |                               |     | 85+30/byte  | μs    |

Figure 7. I2C Timing

# **SPI Interface Timing Characteristics**

SPI Interface Timing for Normal Operating Mode<sup>10</sup>

| Symbol                 | Description                                        | Min | Тур | Max | Units |

|------------------------|----------------------------------------------------|-----|-----|-----|-------|

| Fclk                   | SPI_CLK output clock frequency for normal SPI mode |     | 50  | 75  | MHz   |

| Тѕскн                  | Serial clock high time                             | 9.2 |     |     | ns    |

| T <sub>SCKL</sub>      | Serial clock low time                              | 9.2 |     |     | ns    |

| T <sub>R_SPI_CLK</sub> | SPI_CLK rise time @10mA drive 10pF load            |     |     | 2.8 | ns    |

| T <sub>F_SPI_CLK</sub> | SPI_CLK fall time @10mA drive 10pF load            |     |     | 3.2 | ns    |

| T <sub>CSN_SU</sub>    | CSN output setup time requirement                  | 7   |     |     | ns    |

| T <sub>CSN_HLD</sub>   | CSN output hold time requirement                   | 7   |     |     | ns    |

| T_DO_PD                | Data Output propagation delay                      |     |     | 6   | ns    |

| T <sub>DI_SU</sub>     | Data Input setup time                              | 3   |     |     | ns    |

| T <sub>DI_HLD</sub>    | Data Input hold time                               | 5   |     |     | ns    |

March 2023 - Revision 04d Page 23 of 35 Kinetic Technologies Confidential

<sup>10.</sup> These specifications specify the typical SPI\_CLK output frequency and the minimum requirements of the interface between the SPI NOR Flash device and KTM5030.

## **Interface Description**

#### **UFP AV Interface**

The UFP AV interface consists of 4 highspeed lanes, Auxiliary channel (Side band channel) and HPD out. The highspeed lanes can receive DP audio-video streams or USB data from a source device through DP or USB Type-C link. The high-speed lane mapping is configurable to match the standard DP connector or the USB Type-C connector. The following table shows the KTM5030 high-speed main lanes and side band channel signal mapping for the USB Type-C and DP connector.

| USB TYPE-C |      | STRAIG       | STRAIGHT MAP |              | D MAP        | STD DP |           |     |               |         |  |  |

|------------|------|--------------|--------------|--------------|--------------|--------|-----------|-----|---------------|---------|--|--|

| CONNE      | _    | Assignment C | Assignment D | Assignment C | Assignment D |        | CONNECTOR |     | ***   KTM5030 |         |  |  |

| PIN        | NAME | DP           | DP + USB     | DP_BR        | DP_BR+USB    | PIN    | NAME      | PIN | SIGNAL NAME   | RX PHY  |  |  |

| В8         | SBU2 | AUX_CH_P     | AUX_CH_P     | AUX_CH_N     | AUX_CH_N     | 15     | AUX_CH_P  | D4  | RX_AUXP_SBU2  | AUX CH  |  |  |

| A8         | SBU1 | AUX_CH_N     | AUX_CH_N     | AUX_CH_P     | AUX_CH_P     | 17     | AUX_CH_N  | D3  | RX_AUXN_SBU1  | AUX CH  |  |  |

| B11        | RX1+ | ML2+         | SSRX+        | ML1+         | ML1+         | 12     | ML0_P     | A12 | RX_L0P_SSRX1P | LANE 0  |  |  |

| B10        | RX1- | ML2-         | SSRX-        | ML1-         | ML1-         | 10     | ML0_N     | B12 | RX_L0N_SSRX1N | LAINE U |  |  |

| A2         | TX1+ | ML3+         | SSTX+        | ML0+         | ML0+         | 9      | ML1_P     | A10 | RX_L1P_SSTX1P | LANE1   |  |  |

| A3         | TX1- | ML3-         | SSTX-        | ML0-         | ML0-         | 7      | ML1_N     | B10 | RX_L1N_SSTX1N | LANEI   |  |  |

| В3         | TX2- | ML0-         | ML0-         | ML3-         | SSTX-        | 6      | ML2_P     | B5  | RX_L2P_SSTX2N | LANE 2  |  |  |

| B2         | TX2+ | ML0+         | ML0+         | ML3+         | SSTX+        | 4      | ML2_N     | A5  | RX_L2N_SSTX2P | LAINE Z |  |  |

| A10        | RX2- | ML1-         | ML1-         | ML2-         | SSRX-        | 3      | ML3_P     | В3  | RX_L3P_SSRX2N | LANE 3  |  |  |

| A11        | RX2+ | ML1+         | ML1+         | ML2+         | SSRX+        | 1      | ML3_N     | А3  | RX_L3N_SSRX2P | LAINE 3 |  |  |

If the UFP connector in the system is DP, then all the UFP interface signals are routed to the connector, if the UFP connector is USB Type-C then only the high-speed lanes are routed connector, HPD may connect to the PD controller or remain unused. The AUX signal shall use the AC-coupling capacitors and 1M termination (Pull-up on AUX\_CH\_P and Pull-down on AUX\_CH\_N). The HPD out is a 1.8V TTL signal, it shall use 100K pull-down to GND. The KTM5030 can be powered from the connected DP or USB Type-C source or from an external power supply depending on the application.