# RENESAS

# 10BASE-T/100BASE-TX INTEGRATED PHYCEIVER WITH RMII INTERFACE ICS1894-32

# Description

The ICS1894-32 is a low-power, physical-layer device (PHY) that supports the ISO/IEC 10Base-T and 100Base-TX Carrier-Sense Multiple Access/Collision Detection (CSMA/CD) Ethernet standards, ISO/IEC 8802.3. It is intended for RMII/MII Node applications and includes the Auto-MDIX feature that automatically corrects crossover errors in plant wiring.

The ICS1894-32 incorporates Digital-Signal Processing (DSP) control in its Physical-Medium Dependent (PMD) sub-layer. As a result, it can transmit and receive data on unshielded twisted-pair (UTP) category 5 cables with attenuation in excess of 24 dB at 100MHz.

The ICS1894-32 provides a Serial-Management Interface for exchanging command and status information with a Station-Management (STA) entity. The ICS1894-32 Media-Dependent Interface (MDI) can be configured to provide full-duplex operation at data rates of 10 Mb/s or 100Mb/s.

In addition, the ICS1894-32 includes a programmable LED and interrupt output function. The LED outputs can be configured through registers to indicate the occurance of certain events such as LINK, COLLISION, ACTIVITY, etc. The purpose of the programmable interrupt output is to notify the PHY controller device immediately when a certain event happens instead of having the PHY controller continuously poll the PHY. The events that could be used to generate interrupts are: receiver error, Jabber, page received, parallel detect fault, link partner acknowledge, link status change, auto-negotiation complete, remote fault, collision, etc.

The ICS1894-32 has deep power modes that can result in significant power savings when the link is broken.

**Applications:** NIC cards, PC motherboards, switches, routers, DSL and cable modems, game machines, printers, network connected appliances, and industrial equipment.

# **Features**

- Supports category 5 cables and above with attenuation in excess of 24dB at 100 MHz.

- Single-chip, fully integrated PHY provides PCS, PMA, PMD, and AUTONEG sub layers functions of IEEE standard.

- 10Base-T and 100Base-TX ISO/IEC 8802.3 compliant

- MIIM (MDC/MDIO) management bus for PHY register configuration

- RMII interface support with external 50 MHz system clock

- Single 3.3V power supply

- Highly configurable, supports:

- Media Independent Interface (MII)

- Auto-Negotiation with Parallel detection

- Node applications, managed or unmanaged

- 10M or 100M full duplex modes \*

- Loopback mode for Diagnostic Functions

- Auto-MDI/MDIX crossover correction

- Low-power CMOS (typically 300 mW)

- Power-Down mode (typically 21mW)

- Clock and crystal supported in MII mode

- Programmable LEDs

- Interrupt output pin

- Fully integrated, DSP-based PMD includes:

- Adaptive equalization and baseline-wander correction

- Transmit wave shaping and stream cipher scrambler

- MLT-3 encoder and NRZ/NRZI encoder

- Core power supply (3.3 V)

- 3.3 V/1.8 V VDDIO operation supported

- Smart power control with deep power down feature

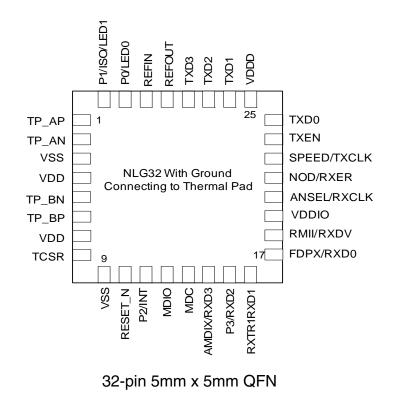

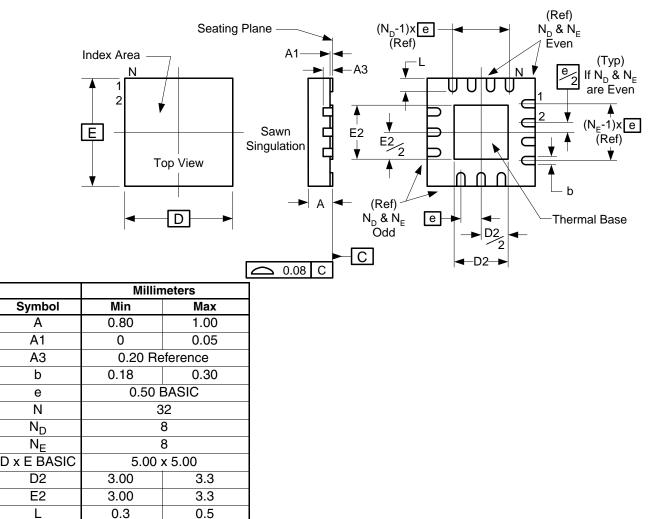

- Available in 32-pin (5mm x 5mm) QFN package, Pb-free

- Available in Industrial Temp and Lead Free

- \* For full/half duplex **RMII** only interface support, please refer to ICS1894-33 datasheet.

- \* For full/half duplex **MII** only interface support, please refer to ICS1894-34 datasheet.

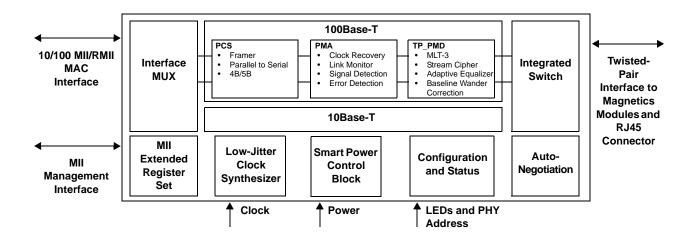

# **Block Diagram**

# **Pin Assignment**

# **Pin Descriptions**

| Pin    | Pin             | Pin               | Pin Description                                                                                                                                                                         |

|--------|-----------------|-------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Number | Name            | Type <sup>1</sup> |                                                                                                                                                                                         |

| 1      | TP_AP           | AIO               | Twisted pair port A (for either transmit or receive) positive signal                                                                                                                    |

| 2      | TP_AN           | AIO               | Twisted pair port A (for either transmit or receive) negative signal                                                                                                                    |

| 3      | VSS             | Ground            | Connect to ground.                                                                                                                                                                      |

| 4      | VDD             | Power             | 3.3V Power Supply                                                                                                                                                                       |

| 5      | TP_BN           | AIO               | Twisted pair port B (for either transmit or receive) negative signal                                                                                                                    |

| 6      | TP_BP           | AIO               | Twisted pair port B (for either transmit or receive) positive signal                                                                                                                    |

| 7      | VDD             | Power             | 3.3V Power Supply                                                                                                                                                                       |

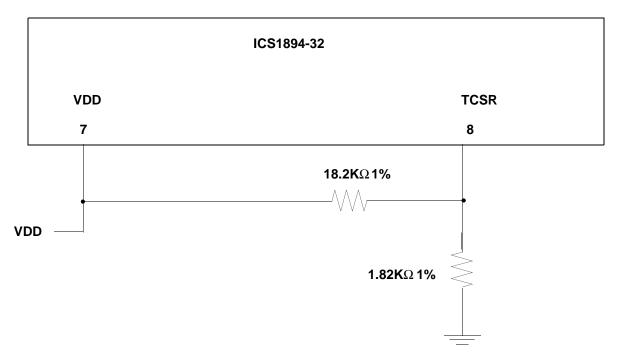

| 8      | TCSR            | AIO               | Transmit Current bias pin, connected to Vdd and ground via resistors (see "Recommended Component Values" table and the "ICS1894-32 TCSR" figure).                                       |

| 9      | VSS             | Ground            | Connect to ground.                                                                                                                                                                      |

| 10     | RESET_N         | Input             | Hardware reset for the entire chip (active low)                                                                                                                                         |

| 11     | P2/INT          | IO/Ipd            | PHY address Bit 2 as input (during power on reset/hardware reset)<br>Interrupt output as output (default active low, can be programmed to active high)                                  |

| 12     | MDIO            | IO                | Management Data Input/Output                                                                                                                                                            |

| 13     | MDC             | Input             | Management Data Clock                                                                                                                                                                   |

| 14     | AMDIX/RXD3      | IO/Ipu            | AMDIX enable as input (during power on reset/hardware reset)<br>Receive data Bit 3 in MII mode as output.                                                                               |

| 15     | P3/RXD2         | IO/lpd            | PHY address Bit 3 as input (during power on reset/hardware reset)<br>Receive data Bit 2 in MII mode as output.                                                                          |

| 16     | RXTRI/<br>RXD1  | IO/Ipd            | RX tri-state enable as input (during power on reset/hardware reset)<br>Receive data Bit 1 in both RMII and MII mode as output.                                                          |

| 17     | FDPX/<br>RXD0   | IO/Ipu            | Full duplex enable as input (during power on reset/hardware reset)<br>Receive data Bit 0 in both RMII and MII mode as output                                                            |

| 18     | RMII/RXDV       | IO/Ipd            | RMII/MII select as input (during power on reset/hardware reset)<br>Receive data valid in MII mode and CRS_DV in RMII mode as output.                                                    |

| 19     | VDDIO           | Power             | 3.3 V/1.8 V IO Power Supply.                                                                                                                                                            |

| 20     | ANSEL/<br>RXCLK | IO/Ipu            | Auto-negotiation enable as input (during power on reset/hardware reset)<br>Receive clock in MII mode as output.                                                                         |

| 21     | NOD/<br>RXER    | IO/Ipd            | Node select as input (during power on reset/hardware reset)<br>Receive error in MII/RMII mode as output<br>It is recommended to always pull this pin low on power-up or hardware reset. |

| 22     | SPEED/<br>TXCLK | IO/Ipu            | 10M/100M select as input (during power on reset/hardware reset)<br>Transmit clock in MII mode as output                                                                                 |

| 23     | TXEN            | Input             | Transmit enable in RMII/MII mode                                                                                                                                                        |

| 24     | TXD0            | Input             | Transmit data Bit 0 in RMII/MII mode                                                                                                                                                    |

| 25     | VDDD            | Power             | 3.3 V Power Supply                                                                                                                                                                      |

| 26     | TXD1            | Input             | Transmit data Bit 1 in RMII/MII mode                                                                                                                                                    |

| 27     | TXT2            | Input             | Transmit data Bit 2 in MII mode                                                                                                                                                         |

| 28     | TXD3            | Input             | Transmit data Bit 3 in MII mode                                                                                                                                                         |

| 29     | REFOUT          | Output            | 25 MHz crystal output, floating in RMII mode                                                                                                                                            |

| 30     | REFIN           | Input             | 25 MHz crystal (or clock) input in MII mode. 50 MHz clock input in RMII mode.                                                                                                           |

| Pin<br>Number | Pin<br>Name | Pin<br>Type <sup>1</sup> | Pin Description                                                                                                                                                                                             |

|---------------|-------------|--------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

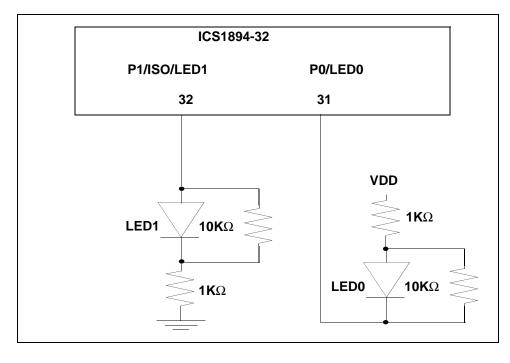

| 31            | P0/LED0     | IO                       | PHY address Bit 0 as input (during power on reset/hardware reset) and LED # 0 (function configurable, default is "activity/no activity") as output                                                          |

| 32            | P1/ISO/LED1 | IO                       | PHY address Bit 1 as input (during power on reset/hardware reset) and LED # 1 (function configurable, default is "10/100 mode") as output; After latch, alternates as a real time receiver isolation input. |

| PADDLE        | VSS         | Ground                   | Connect to ground.                                                                                                                                                                                          |

#### Notes:

- 1. AIO: Analog input/output PAD.

- IO: Digital input/output.

IN/Ipu: Digital input with internal 20k pull-up.

IN/Ipd: Digital input with internal 20k pull-down.

- IO/Ipu: Digital input/output with internal 20k pull-up.

- IO/Ipd: Digital input/output with internal 20k pull-down.

- 2. MII Rx Mode: The RXD[3..0] bits are synchronous with RXCLK. When RXDV is asserted, RXD[3..0] presents valid data to MAC on the MII interface. RXD[3..0] is invalid when RXDV is de-asserted.

- 3. RMII Rx Mode: The RXD[1:0] bits are synchronous with REFIN. For each clock period in which CRS\_DV is asserted, two bits of recovered data are sent from the PHY to the MAC.

- 4. MII Tx Mode: The TXD[3..0] bits are synchronous with TXCLK. When TXEN is asserted, TXD[3..0] presents valid data from the MAC on the MII interface. TXD[3..0] has no effect when TXEN is de-asserted.

4

5. RMII Tx Mode: The TXD[1:0] bits are synchronous with REFIN. For each clock period in which TX\_EN is asserted, two bits of data are received by the PHY from the MAC.

© 2019 Renesas Electronics Corporation

# **Strapping Options**

| Pin<br>Number | Pin<br>Name     | Pin<br>Type <sup>1</sup> | Pin Function                                                                                  |

|---------------|-----------------|--------------------------|-----------------------------------------------------------------------------------------------|

| 14            | AMDIX/RXD3      | IO/Ipu                   | 1 = AMDIX enable<br>0 = AMDIX disable                                                         |

| 15            | <b>P3</b> /RXD2 | IO/Ipd                   | The PHY address is set by P[3:0] at power-on reset. P0 and P1 must have external              |

| 11            | P2/INT          | IO/Ipd                   | pull-up or pull-down to set address at start up.                                              |

| 31            | <b>P0</b> /LED0 | IO                       |                                                                                               |

| 32            | P1/ISO/LED1     | IO                       |                                                                                               |

| 16            | RXTRI/RXD1      | IO/Ipd                   | 1 = Real time receiver isolation function enable <sup>3</sup> ; 0 = Receiver Tristate Disable |

| 17            | FDPX/RXD0       | IO/Ipu                   | 1=Full duplex<br>0=Half duplex (mode not supported)<br>Ignored if Auto negotiation is enabled |

| 18            | RMII/RXDV       | IO/Ipd                   | 1 = RMII mode<br>0 = MII mode                                                                 |

| 20            | ANSEL/RXCLK     | IO/Ipu                   | 1=Enable auto negotiation<br>0=Disable auto negotiation                                       |

| 21            | NOD/RXER        | IO/Ipd                   | 0=Node mode<br>1=repeater mode (mode not supported)                                           |

| 22            | SPEED/TXCLK     | IO/Ipu                   | 1=100M mode<br>0=10M mode<br>Ignored if Auto negotiation is enabled                           |

1. IO/Ipu = Digital Input with internal 20k pull-up during power on reset/hardware reset; output pin otherwise.

**2.** IO/Ipd = Digital Input with internal 20k pull-down during power on reset/hardware reset; output pin otherwise.

3. If RXTRI/RXD1 pin is latched high during power on reset/hardware reset, P1/ISO/LED1 functions as RX real time isolation control input after latch and LED1 function will be disabled.

# **Functional Description**

The ICS1894-32 is an ethernet PHYceiver. During data transmission, it accepts sequential nibbles/di-bits from the MAC (Media Access Control), converts them into a serial bit stream, encodes them, and transmits them over the medium through an external isolation transformer. When receiving data, the ICS1894-32 converts and decodes a serial bit stream (acquired from an isolation transformer that interfaces with the medium) into sequential nibbles/di-bits. It subsequently presents these nibbles/di-bits to the MAC Interface.

The ICS1894-32 implements the OSI model's physical layer, consisting of the following, as defined by the ISO/IEC 8802-3 standard:

- Physical Coding sublayer (PCS)

- Physical Medium Attachment sublayer (PMA)

- Physical Medium Dependent sublayer (PMD)

- Auto-Negotiation sublayer

5

The ICS1894-32 is transparent to the next layer of the OSI model, the link layer. The link layer has two sublayers: the Logical Link Control sublayer and the MAC sublayer. The ICS1894-32 can interface directly with the MAC via MII/RMII interface signals.

The ICS1894-32 transmits framed packets acquired from its MAC Interface and receives encapsulated packets from another PHY, which it translates and presents to its MAC Interface.

**Note:** As per the ISO/IEC standard, the ICS1894-32 does not affect, nor is it affected by, the underlying structure of the MAC frame it is conveying.

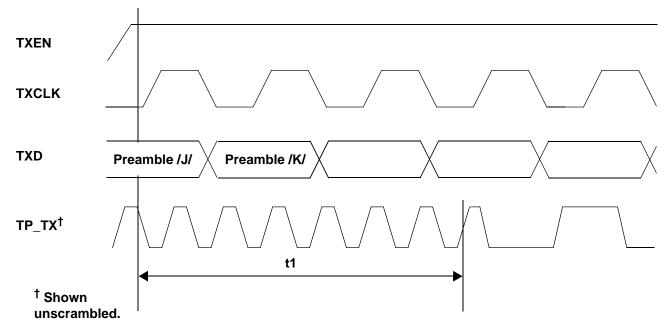

#### **100Base-TX Operation**

During 100Base-TX data transmission, the ICS1894-32 accepts packets from the MAC and inserts Start-of-Stream Delimiters (SSDs) and End-of-Stream Delimiters (ESDs) into the data stream. The ICS1894-32 encapsulates each MAC frame, including the preamble, with an SSD and an ESD. As per the ISO/IEC Standard, the ICS1894-32 replaces the first octet of each MAC preamble with an SSD and appends an ESD to the end of each MAC frame.

When receiving data from the medium, the ICS1894-32 removes each SSD and replaces it with the pre-defined preamble pattern before presenting the data on the MAC Interface. When the ICS1894-32 encounters an ESD in the received data stream, signifying the end of the frame, it ends the presentation of data on the MAC Interface. Therefore, the local MAC receives an unaltered copy of the transmitted frame sent by the remote MAC.

During periods when MAC frames are being neither transmitted nor received, the ICS1894-32 signals and detects the IDLE condition on the Link Segment. In the 100Base-TX mode, the ICS1894-32 transmit channel sends a continuous stream of scrambled ones to signify the IDLE condition. Similarly, the ICS1894-32 receive channel continually monitors its data stream and looks for a pattern of scrambled ones. The results of this signaling and monitoring provide the ICS1894-32 with the means to establish the integrity of the Link Segment between itself and its remote link partner and inform its Station Management Entity (SME) of the link status.

#### **10Base-T Operation**

During 10Base-T data transmission, the ICS1894-32 inserts only the IDL delimiter into the data stream. The ICS1894-32 appends the IDL delimiter to the end of each MAC frame. However, since the 10Base-T preamble already has a Start-of-Frame delimiter (SFD), it is not required that the ICS1894-32 insert an SSD-like delimiter.

When receiving data from the medium (such as a twisted-pair cable), the ICS1894-32 uses the preamble to synchronize its receive clock. When the ICS1894-32

receive clock establishes lock, it presents the preamble nibbles to the MAC Interface.

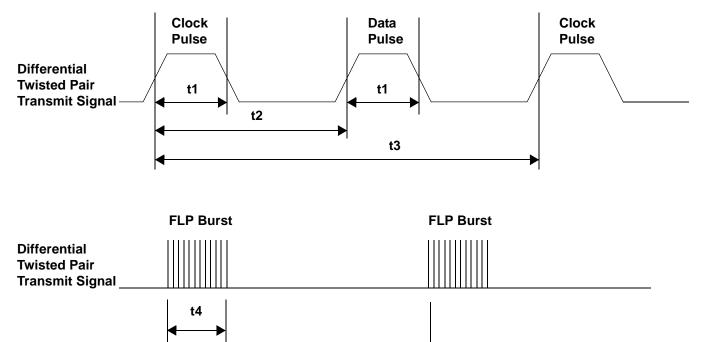

In 10M operations, during periods when MAC frames are being neither transmitted nor received, the ICS1894-32 signals and detects Normal Link Pulses. This action allows the integrity of the Link Segment with the remote link partner to be established and then reported to the ICS1894-32's SME.

#### **Auto-Negotiation**

The ICS1894-32 conforms to the auto-negotiation protocol, defined in Clause 28 of the IEEE 802.3u specification. Autonegotiation is enabled by either hardware pin strapping (pin 20) or software (register 0h bit 12).

Auto-negotiation allows link partners to select the highest common mode of operation. Link partners advertise their capabilities to each other, and then compare their own capabilities with those they received from their link partners. The highest speed and duplex setting that is common to the two link partners is selected as the mode of operation.

The following list shows the speed and duplex operation mode from highest to lowest.

- Priority 1: 100Base-TX, full-duplex

- Priority 2: 100Base-TX, half-duplex

- Priority 3: 10Base-T, full-duplex

- Priority 4: 10Base-T, half-duplex

If auto-negotiation is not supported or the ICS1894-32 link partner is forced to bypass auto-negotiation, the ICS1894-32 sets its operating mode by observing the signal at its receiver. This is known as parallel detection, and allows the ICS1894-32 to establish link by listening for a fixed signal protocol in the absence of auto-negotiation advertisement protocol.

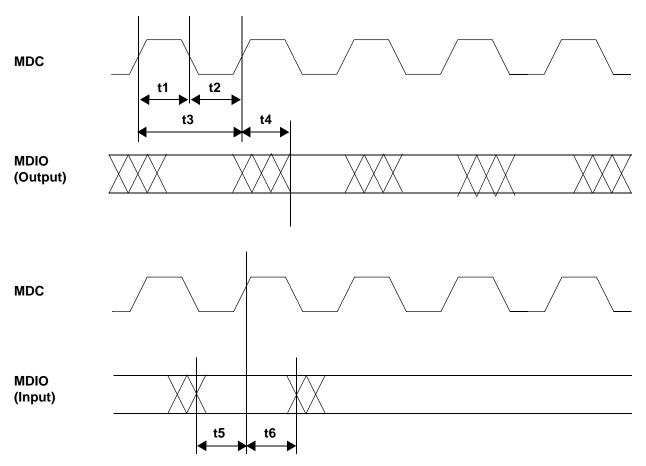

#### **MII Management (MIIM) Interface**

6

The ICS1894-32 supports the IEEE 802.3 MII Management Interface, also known as the Management Data Input / Output (MDIO) Interface. This interface allows upper-layer devices to monitor and control the state of the ICS1894-32. An external device with MIIM capability is used to read the PHY status and/or configure the PHY settings. Additional details on the MIIM interface can be found in Clause 22.2.4.5 of the IEEE 802.3u Specification. The MIIM interface consists of the following:

- A physical connection that incorporates the clock line (MDC) and the data line (MDIO).

- A specific protocol that operates across the aforementioned physical connection that allows an external controller to communicate with one or more ICS1894-32 devices. Each ICS1894-32 device is assigned a PHY address between 1 and 7 by the P[4:0] strapping pins. P3 and P4 address bits are hardcoded to '0' in design.

- An internal addressable set of thirty-one 8-bit MDIO registers. Register [0:6] are required, and their functions are defined by the IEEE 802.3u Specification. The additional registers are provided for expanded functionality.

The ICS1894-32 supports MIIM in both MII mode and RMII mode.

The following table shows the MII Management frame format for the ICS1894-32.

#### **MII Management Frame Format**

|       | Preamble | Start of<br>Frame | Read/Write<br>OP Code | PHY Address<br>Bits [4:0] | REG Address<br>Bits [4:0] | ТА | Data Bits<br>[15:0] | ldle |

|-------|----------|-------------------|-----------------------|---------------------------|---------------------------|----|---------------------|------|

| Read  | 32 1's   | 01                | 10                    | 00AAA                     | RRRRR                     | Z0 | DDDDDDDD_DDDDDDD    | Z    |

| Write | 32 1's   | 01                | 01                    | 00AAA                     | RRRRR                     | 10 | DDDDDDD_DDDDDDD     | Z    |

7

## Interrupt (INT)

P2/INT (pin 11) is an optional interrupt signal that is used to inform the external controller that there has been a status update in the ICS1894-32 PHY register. Register 23 shows the status of the various interrupts while register 22 controls the enabling/disabling of the interrupts.

#### **MII Data Interface**

The Media Independent Interface (MII) is specified in Clause 22 of the IEEE 802.3u Specification. It provides a common interface between physical layer and MAC layer devices, and has the following key characteristics:

- Supports 10Mbps and 100Mbps data rates.

- Uses a 25MHz reference clock, sourced by the PHY.

- Provides independent 4-bit wide (nibble) transmit and receive data paths.

- Contains two distinct groups of signals: one for transmission and the other for reception.

The ICS1894-32 is configured for MII mode upon power-up or hardware reset with the following:

A 25MHz crystal connected to REFIN, REFOUT (pins 30, 29), or an external 25MHz clock source (oscillator) connected to REFIN

### **MII Signal Definition**

The following table describes the MII signals. Refer to Clause 22 of the IEEE 802.3u Specification for detailed information.

| MII Signal Name | Direction<br>(with respect to PHY,<br>ICS1894-32 signal) | Direction<br>(with respect to MAC) | Description                                              |

|-----------------|----------------------------------------------------------|------------------------------------|----------------------------------------------------------|

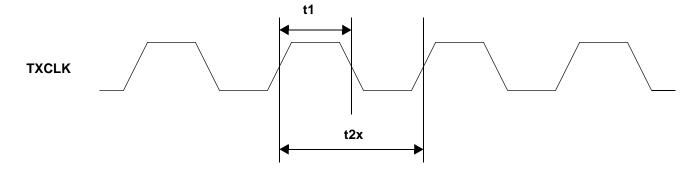

| TXCLK           | Output                                                   | Input                              | Transmit Clock<br>(2.5MHz for 10Mbps; 25MHz for 100Mbps) |

| TXEN            | Input                                                    | Output                             | Transmit Enable                                          |

| TXD[3:0]        | Input                                                    | Output                             | Transmit Data [3:0]                                      |

| RXCLK           | Output                                                   | Input                              | Receive Clock<br>(2.5MHz for 10Mbps; 25MHz for 100Mbps)  |

| RXDV            | Output                                                   | Input                              | Receive Data Valid                                       |

| RXD[3:0]        | Output                                                   | Input                              | Receive Data [3:0]                                       |

| RXER            | Output                                                   | Input, or (not required)           | Receive Error                                            |

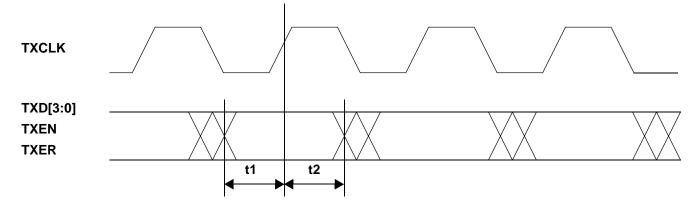

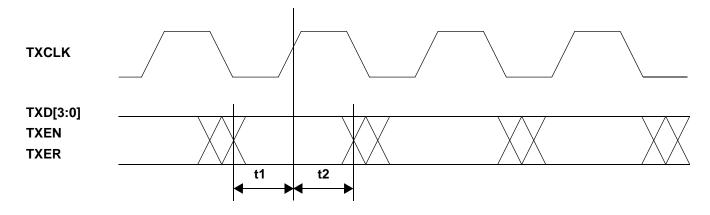

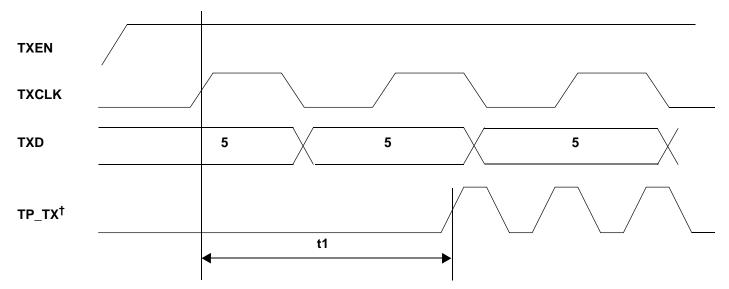

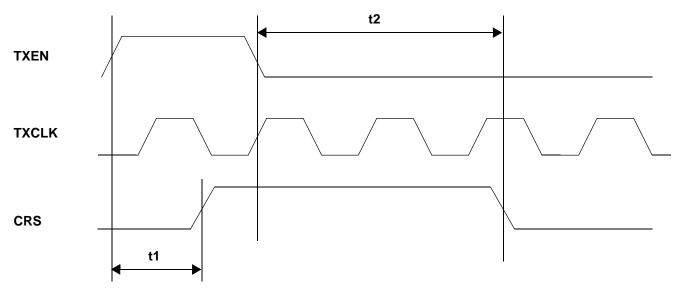

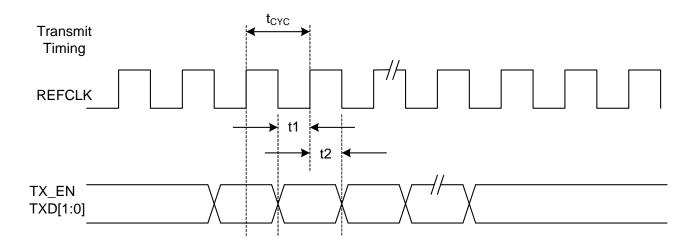

## Transmit Clock (TXCLK)

TXCLK is sourced by the PHY. It is a continuous clock that provides the timing reference for TXEN and TXD[3:0]. TXCLK is 2.5MHz for 10Mbps operation and 25MHz for 100Mbps operation.

# Transmit Enable (TXEN)

TXEN indicates the MAC is presenting nibbles on TXD[3:0] for transmission. It is asserted synchronously with the first nibble of the preamble and remains asserted while all nibbles to be transmitted are presented on the MII, and is negated prior to the first TXCLK following the final nibble of a frame. TXEN transitions synchronously with respect to TXCLK.

# Transmit Data (TXD[3:0])

TXD[3:0] transitions synchronously with respect to TXCLK. When TXEN is asserted, TXD[3:0] are accepted for transmission by the PHY. TXD[3:0] is "00" to indicate idle when TXEN is de-asserted. Values other than "00" on TXD[3:0] while TXEN is de-asserted are ignored by the PHY.

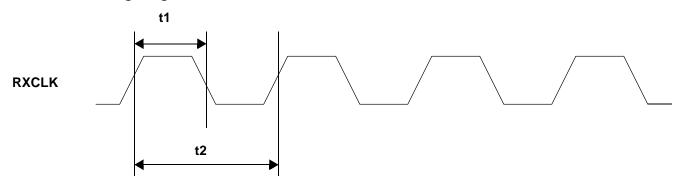

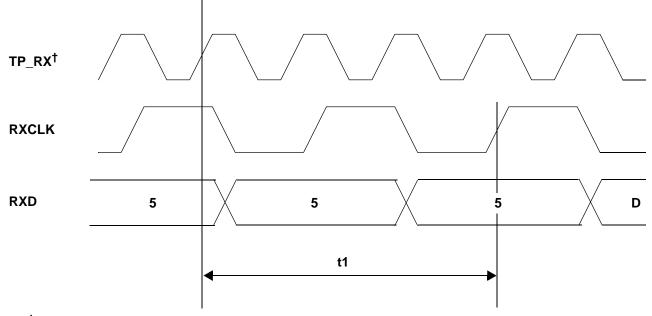

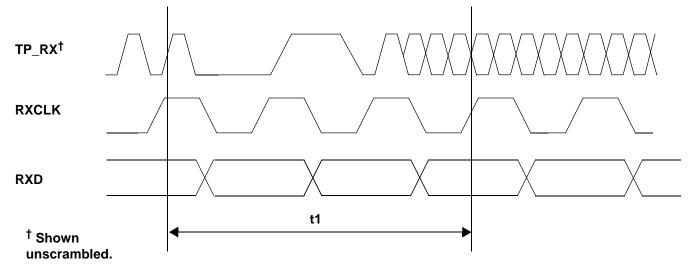

# **Receive Clock (RXCLK)**

RXCLK provides the timing reference for RXDV, RXD[3:0], and RXER.

- In 10Mbps mode, RXCLK is recovered from the line while carrier is active. RXCLK is derived from the PHY's reference clock when the line is idle, or link is down.

- In 100Mbps mode, RXCLK is continuously recovered from the line. If link is down, RXCLK is derived from the PHY's reference clock.

RXCLK is 2.5MHz for 10Mbps operation and 25MHz for 100Mbps operation.

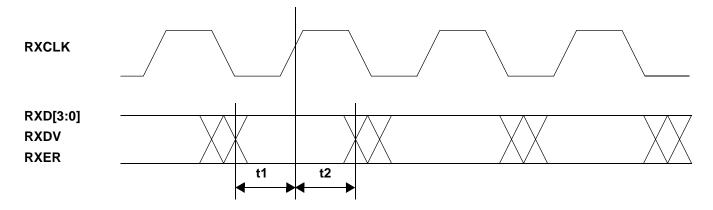

# **Receive Data Valid (RXDV)**

RXDV is driven by the PHY to indicate that the PHY is presenting recovered and decoded nibbles on RXD[3:0].

- In 10Mbps mode, RXDV is asserted with the first nibble of the SFD (Start of Frame Delimiter), and remains asserted until the end of the frame.

- In 100Mbps mode, RXDV is asserted from the first nibble of the preamble to the last nibble of the frame.

RXDV transitions synchronously with respect to RXCLK.

# Receive Data (RXD[3:0])

RXD[3:0] transitions synchronously with respect to RXC. For each clock period in which RXDV is asserted, RXD[3:0] transfers a nibble of recovered data from the PHY.

# **Receive Error (RXER)**

8

RXER is asserted for one or more RXCLK periods to indicate that an error (e.g. a coding error or any error that a

PHY is capable of detecting, and that may otherwise be undetectable by the MAC sub-layer) was detected somewhere in the frame presently being transferred from the PHY. RXER transitions synchronously with respect to RXC. While RXDV is de-asserted, RXER has no effect on the MAC.

#### Reduced MII (RMII) Data Interface

The Reduced Media Independent Interface (RMII) specifies a low pin count Media Independent Interface (MII). It provides a common interface between physical layer and MAC layer devices, and has the following key characteristics:

- Supports 10Mbps and 100Mbps data rates.

- Uses a single 50MHz reference clock provided by the MAC or the system board.

- Provides independent 2-bit wide (di-bit) transmit and receive data paths.

- Contains two distinct groups of signals: one for transmission and the other for reception.

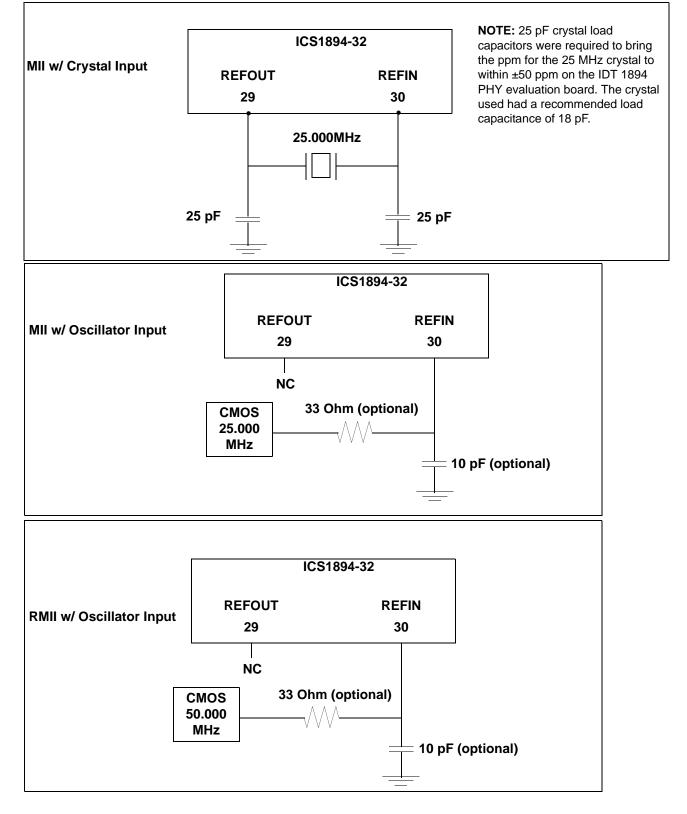

In RMII mode, a 50 MHz reference clock is connected to REFIN(pin 30).

#### **RMII Signal Definition**

The following table describes the RMII signals. Refer to RMII Specification for detailed information.

| RMII Signal Name | Direction<br>(with respect to PHY,<br>ICS1894-32 signal) | Direction<br>(with respect to MAC) | Description                                                                    |

|------------------|----------------------------------------------------------|------------------------------------|--------------------------------------------------------------------------------|

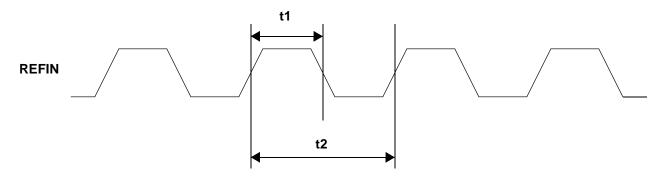

| REFIN            | Input                                                    | Input or Output                    | Synchronous 50 MHz clock reference for receive, transmit and control interface |

| TX_EN            | Input                                                    | Output                             | Transmit Enable                                                                |

| TXD[1:0]         | Input                                                    | Output                             | Transmit Data [1:0]                                                            |

| RXD[1:0          | Output                                                   | Input                              | Receive Data [1:0]                                                             |

| RX_ER            | Output                                                   | Input, or (not required)           | Receive Error                                                                  |

| CRS_DV[RXDV]     | Output                                                   | Input                              | Carrier Sense/Data Valid                                                       |

#### **Reference Clock (REFIN)**

REFIN is sourced by the MAC or system board. It is a continuous 50MHz clock that provides the timing reference for TX\_EN, TXD[1:0], CRS\_DV, RXD[1:0], and RX\_ER.

#### Transmit Enable (TX\_EN)

TX\_EN indicates that the MAC is presenting di-bits on TXD[1:0] for transmission. It is asserted synchronously with the first nibble of the preamble and remains asserted while all di-bits to be transmitted are presented on the RMII, and is negated prior to the first REFIN following the final di-bit of a frame. TX\_EN transitions synchronously with respect to REFIN.

#### Transmit Data [1:0] (TXD[1:0])

TXD[1:0] transitions synchronously with respect to REFIN. When TX\_EN is asserted, TXD[1:0] are accepted for transmission by the PHY. TXD[1:0] is "00" to indicate idle when TX\_EN is de-asserted. Values other than "00" on TXD[1:0] while TX\_EN is de-asserted are ignored by the PHY.

#### Carrier Sense/Data Valid (CRS\_DV[RXDV])

CRS\_DV, identified as RXDV (pin 18), shall be asserted by the PHY when the receive medium is non-idle. The specifics of the definition of idle for 10BASE-T and 100BASE-X are contained in IEEE 802.3 [1] and IEEE 802.3u [2]. CRS\_DV is asserted asynchronously on detection of carrier due to the criteria relevant to the operating mode. That is, in 10BASE-T mode, when squelch is passed or in 100BASE-X mode when 2 non-contiguous zeroes in 10 bits are detected carrier is said to be detected. Loss of carrier shall result in the deassertion of CRS DV synchronous to the cycle of REFIN which presents the first di-bit of a nibble onto RXD[1:0] (i.e. CRS DV is deasserted only on nibble boundaries). If the PHY has additional bits to be presented on RXD[1:0] following the initial deassertion of CRS DV, then the PHY shall assert CRS DV on cycles of REFIN which present the second di-bit of each nibble and deassert CRS DV on cycles of REFIN which present the first di-bit of a nibble. The result is: Starting on nibble boundaries CRS DV toggles at 25 MHz in 100Mb/s mode and 2.5 MHz in 10Mb/s mode when the Carrier event ends before the RX DV signal internal to the PHY is deasserted (i.e. the FIFO still has bits to transfer when the carrier event ends.) Therefore, the MAC can accurately recover RX DV and the Carrier event end time. During a false carrier event, CRS DV shall remain asserted for the duration of carrier activity.

The data on RXD[1:0] is considered valid once CRS\_DV is asserted. However, since the assertion of CRS\_DV is asynchronous relative to REFIN, the data on RXD[1:0] shall be "00" until proper receive signal decoding takes place (see definition of RXD[1:0] behavior).

\***Note:** CRS\_DV is asserted asynchronously in order to minimize latency of control signals through the PHY.

#### Receive Data [1:0] (RXD[1:0])

10

RXD[1:0] transitions synchronously to REFIN. For each clock period in which CRS\_DV is asserted, RXD[1:0] transfers two bits of recovered data from the PHY. RXD[1:0] is "00" to indicate idle when CRS\_DV is de-asserted. Values other than "00" on RXD[1:0] while CRS\_DV is de-asserted

are ignored by the MAC.

## **Receive Error (RX\_ER)**

RX\_ER is asserted for one or more REFIN periods to indicate that an error (e.g. a coding error or any error that a PHY is capable of detecting, and that may otherwise be undetectable by the MAC sub-layer) was detected somewhere in the frame presently being transferred from the PHY. RX\_ER transitions synchronously with respect to REFIN. While CRS\_DV is de-asserted, RX\_ER has no effect on the MAC.

# Auto-MDI/MDIX Crossover

The ICS1894-32 includes the auto-MDI/MDIX crossover feature. In a typical CAT 5 Ethernet installation the transmit twisted pair signal pins of the RJ45 connector are crossed over in the CAT 5 wiring to the partners receive twisted pair signal pins and receive twisted pair to the partners transmit twisted pair. This is usually accomplished in the wiring plant. Hubs generally wire the RJ45 connector crossed to accomplish the crossover. Two types of CAT 5 cables (straight and crossed) are available to achieve the correct connection. The Auto-MDI/MDIX feature automatically corrects for miss-wired installations by automatically swapping transmit and receive signal pairs at the PHY when no link results. Auto-MDI/MDIX is automatic, but may be disabled for test purposes by writing MDIO register 19 Bits 9:8 in the MDIO register. The Auto-MDI/MDIX function is independent of Auto-Negotiation and preceeds Auto-Negotiation when enabled.

#### Auto MDI/MDIX Table

| AMDIX_EN<br>(pin 14) | AMDIX_EN<br>[Reg 19:9] | MDI_MODE<br>[Reg 19:8] | Tx/Rx MDI<br>Configuration   |

|----------------------|------------------------|------------------------|------------------------------|

| х                    | 0                      | 0                      | straight                     |

| х                    | 0                      | 1                      | cross                        |

| 0                    | 1                      | х                      | straight                     |

| 1                    | 1                      | X                      | straight/cross (auto select) |

| Default              | •                      |                        |                              |

| 1                    | 1                      | 0                      | straight/cross (auto select) |

#### Definitions:

straight

transmit = TP\_AP & TP\_AN receive = TP\_BP & TP\_BN cross transmit = TP\_BP & TP\_BN receive = TP\_AP & TP\_AN AMDIX\_EN (Pin 14) AMDIX enable pin with 20 kOhm pull-up resistor AMDIX\_EN [19:9] MDIO register 19h bit 9 MDI MODE [19:8] MDIO register 19h bit 8

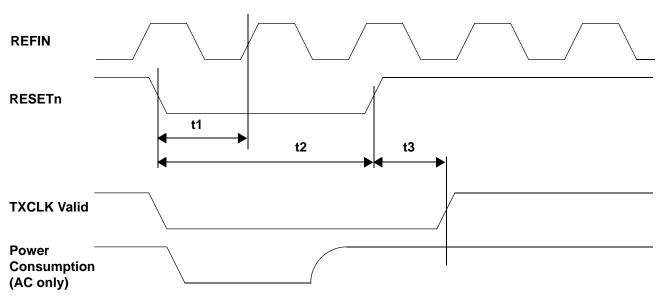

The ICS1894-32 supports a Deep Power Mode (DPD) that is enabled under the following conditions:

1. The Phy is not Receiving any signal from the partner (Link Down)

2. The MAC is not transmitting data to the Phy (TXEN Low)

Once the above conditions are met, the Phy goes into DPD mode after 32s (typical).

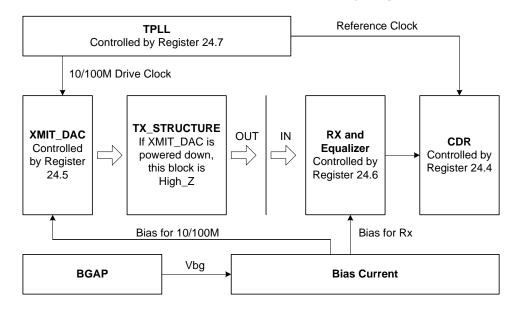

The logic internal to the device can be selectively shut down in DPD mode depending on Register 24 Bits 8-4.

#### Block Diagram of the Different Sections of the PHY as Affected by Register 24 bits

12

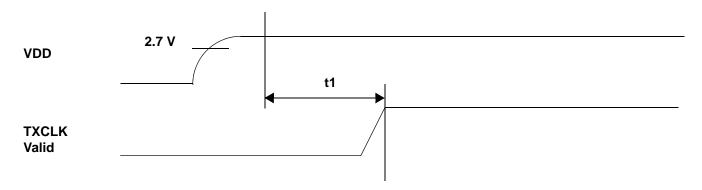

# **Clock Reference Interface**

© 2019 Renesas Electronics Corporation

The REFIN pin provides the ICS1894-32 Clock Reference Interface. The ICS1894-32 requires a single clock reference with a frequency of 25 MHz ±50 parts per million. This accuracy is necessary to meet the interface requirements of the ISO/IEEE 8802-3 standard, specifically clauses 22.2.2.1 and 24.2.3.4. The ICS1894-32 supports two clock source configurations: a CMOS oscillator or a CMOS driver. The input to REFIN is CMOS (10% to 90% VDD), not TTL. Alternately, a 25MHz crystal may be used.

#### **Crystal or Oscillator Connection**

If a crystal is used as the clocking source, connect it to both the REFIN (pin 30) and REFOUT (pin 29) pins of the ICS1894-32. A pair of bypass capacitors on either side of the crystal are connected to ground. The crystal is used in the parallel resonance or anti-resonance mode. The value of the load caps serve to adjust the final frequency of the crystal oscillation. Typical applications would use 25 pF load caps. The exact value will be affected by the board routing capacitance on REFIN and REFOUT pins. Smaller load capacitors raise the frequency of oscillation. Once the exact value of load capacitance is established it will be the same for all boards using the same specification crystal. The best way to measure the crystal frequency is to measure the frequency of TXCLK (pin 22) using a frequency counter with a 1 second gate time. Using the buffered output TXCLK prevents the crystal frequency from being affected by the measurement. The crystal specification is shown in the *25MHz Crystal Specification* table.

#### 25 MHz Crystal Specification Table

| Specifications        | Symbol       | Minimum  | Typical  | Maximum  | Unit |

|-----------------------|--------------|----------|----------|----------|------|

| Fundamental Frequency | F0           | 24.99875 | 25.00000 | 25.00125 | MHz  |

| Freq. Tolerance       | $\Delta$ F/f |          |          | ±50      | ppm  |

| Input Capacitance     | Cin          |          | 3        |          | pF   |

#### 25 MHz Oscillator Specification table

| Specifications                     | Symbol       | Minimum  | Typical  | Maximum  | Unit  |

|------------------------------------|--------------|----------|----------|----------|-------|

| Output Frequency                   | F0           | 24.99875 | 25.00000 | 25.00125 | MHz   |

| Freq. Stability (including aging)  | $\Delta$ F/f |          |          | ±50      | ppm   |

| Duty cycle CMOS level one-half VDD | Tw/T         | 35       |          | 65       | %     |

| VIH                                |              | 2.79     |          |          | Volts |

| VIL                                |              |          |          | 0.33     | Volts |

#### 50 MHz Oscillator Specification table

| Specifications                     | Symbol       | Minimum | Typical  | Maximum | Unit  |

|------------------------------------|--------------|---------|----------|---------|-------|

| Output Frequency                   | F0           | 49.9975 | 50.00000 | 50.0025 | MHz   |

| Freq. Stability (including aging)  | $\Delta$ F/f |         |          | ±50     | ppm   |

| Duty cycle CMOS level one-half VDD | Tw/T         | 35      |          | 65      | %     |

| VIH                                |              | 2.79    |          |         | Volts |

| VIL                                |              |         |          | 0.33    | Volts |

#### **Status Interface**

The ICS1894-32 has two multi-function configuration pins that report the PHY status by providing signals that are intended for driving LEDs. Configuration is set by Bank0 Register 20.

#### Pins for Monitoring the Data Link table

| Pin         | Status Events that drive the LEDs       |

|-------------|-----------------------------------------|

| P0/LED0     | Link, Activity, Tx, Rx, COL, Mode, Dplx |

| P1/ISO/LED1 | Link, Activity, Tx, Rx, COL, Mode, Dplx |

#### Note:

1. During either power-on reset or hardware reset, each multi-function configuration pin is an input that is sampled when the ICS1894-32 exits the reset state. After sampling is complete, these pins are output pins that can drive status LEDs.

2. A software reset does not affect the state of a multi-function configuration pin. During a software reset, all multi-function configuration pins are outputs.

3. Each multi-function configuration pin must be pulled either up or down with a resistor to establish the address of the ICS1894-32. LEDs may be placed in series with these resistors to provide a designated status indicator as described in the *Pins for Monitoring the Data Link* table. Use  $1K\Omega$  resistors.

**Caution:** Pins listed in the *Pins for Monitoring the Data Link* table must not float.

4. As outputs, the asserted state of a multi-function configuration pin is the inverse of the sense sampled during reset. This inversion provides a signal that can illuminate an LED during an asserted state. For example, if a multi-function configuration pin is pulled down to ground through an LED and a current-limiting resistor, then the sampled sense of the input is low. To illuminate this LED for the asserted state, the output is driven high.

5. Adding 10K $\Omega$  resistors across the LEDs ensures the PHY address is fully defined during slow VDD power-ramp conditions.

6. PHY address 00 tri-states the MII interface. (Do not select PHY address 00 unless you want the MII tri-stated.)

The following figure shows typical biasing and LED connections for the ICS1894-32.

The above circuit decodes the PHY address = 1

# **Register Map**

| Register Address | Register Name                                   | Basic / Extended |

|------------------|-------------------------------------------------|------------------|

| 0                | Control                                         | Basic            |

| 1                | Status                                          | Basic            |

| 2,3              | PHY Identifier                                  | Extended         |

| 4                | Auto-Negotiation Advertisement                  | Extended         |

| 5                | Auto-Negotiation Link Partner Ability           | Extended         |

| 6                | Auto-Negotiation Expansion                      | Extended         |

| 7                | Auto-Negotiation Next Page Transmit             | Extended         |

| 8                | Auto-Negotiation Next Page Link Partner Ability | Extended         |

| 9 through 15     | Reserved by IEEE                                | Extended         |

| 16 through 31    | Vendor-Specific (IDT) Registers                 | Extended         |

# **Register Description**

| Bit      | Definition                | When Bit = 0                             | When Bit = 1             | Access <sup>2</sup> | SF <sup>2</sup> | Default <sup>3</sup> | Hex  |

|----------|---------------------------|------------------------------------------|--------------------------|---------------------|-----------------|----------------------|------|

| Register | 0 - Control               |                                          |                          |                     |                 |                      |      |

| 0.15     | Reset                     | No effect                                | Reset mode               | RW                  | SC              | 0                    | 3    |

| 0.14     | Loopback enable           | Disable Loopback mode                    | Enable Loopback mode     | RW                  | -               | 0                    |      |

| 0.13     | Speed select <sup>1</sup> | 10 Mbps operation                        | 100 Mbps operation       | RW                  | -               | 1                    |      |

| 0.12     | Auto-Negotiation enable   | Disable Auto-Negotiation                 | Enable Auto-Negotiation  | RW                  | -               | 1                    |      |

| 0.11     | Low-power mode            | Normal power mode                        | Low-power mode           | RW                  | -               | 0                    | 1/5‡ |

| 0.10     | Isolate                   | No effect                                | Isolate from MII         | RW                  | -               | 0/1‡                 |      |

| 0.9      | Auto-Negotiation restart  | No effect                                | Restart Auto-Negotiation | RW                  | SC              | 0                    |      |

| 0.8      | Duplex mode <sup>1</sup>  | Half-duplex operation mode not supported | Full-duplex operation    | RW                  | -               | 1                    | _    |

| 0.7      | —                         | —                                        | —                        | RW                  | -               | 0                    | 0    |

| 0.6      | IEEE reserved             | Always 0                                 | N/A                      | RO                  | -               | 0†                   |      |

| 0.5      | IEEE reserved             | Always 0                                 | N/A                      | RO                  | -               | 0†                   |      |

| 0.4      | IEEE reserved             | Always 0                                 | N/A                      | RO                  | -               | 0†                   |      |

| 0.3      | IEEE reserved             | Always 0                                 | N/A                      | RO                  | -               | 0†                   | 0    |

| 0.2      | IEEE reserved             | Always 0                                 | N/A                      | RO                  | -               | 0†                   |      |

| 0.1      | IEEE reserved             | Always 0                                 | N/A                      | RO                  | -               | 0†                   |      |

| 0.0      | IEEE reserved             | Always 0                                 | N/A                      | RO                  | -               | 0†                   |      |

16

IDT® 10BASE-T/100BASE-TX INTEGRATED PHYCEIVER WITH RMII INTERFACE

| Bit      | Definition                | When Bit = 0                               | When Bit = 1                                  | Access <sup>2</sup> | SF <sup>2</sup> | Default <sup>3</sup> | Hex |

|----------|---------------------------|--------------------------------------------|-----------------------------------------------|---------------------|-----------------|----------------------|-----|

| Register | 1 - Control               |                                            |                                               |                     | . 1             |                      |     |

| 1.15     | 100Base-T4                | Always 0. (Not supported.)                 | N/A                                           | RO                  | -               | 0                    | 7   |

| 1.14     | 100Base-TX full duplex    | Mode not supported                         | Mode supported                                | CW                  | _               | 1                    |     |

| 1.13     | —                         | —                                          | —                                             | CW                  | _               | 1                    | ]   |

| 1.12     | 10Base-T full duplex      | Mode not supported                         | Mode supported                                | CW                  | _               | 1                    |     |

| 1.11     | —                         | —                                          | —                                             | CW                  | _               | 1                    | 8   |

| 1.10     | IEEE reserved             | Always 0                                   | N/A                                           | CW                  | -               | 0†                   |     |

| 1.9      | IEEE reserved             | Always 0                                   | N/A                                           | CW                  | _               | 0†                   |     |

| 1.8      | IEEE reserved             | Always 0                                   | N/A                                           | CW                  | _               | 0†                   | ]   |

| 1.7      | IEEE reserved             | Always 0                                   | N/A                                           | CW                  | _               | 0†                   | 0   |

| 1.6      | MF Preamble suppression   | PHY requires MF<br>Preambles               | PHY does not require MF<br>Preambles          | RO                  | _               | 0                    |     |

| 1.5      | Auto-Negotiation complete | Auto-Negotiation is in process, if enabled | Auto-Negotiation is<br>completed              | RO                  | LH              | 0                    |     |

| 1.4      | Remote fault              | No remote fault detected                   | Remote fault detected                         | RO                  | LH              | 0                    |     |

| 1.3      | Auto-Negotiation ability  | N/A                                        | Always 1: PHY has<br>Auto-Negotiation ability | RO                  | —               | 1                    | 9   |

| 1.2      | Link status               | Link is invalid/down                       | Link is valid/established                     | RO                  | LL              | 0                    |     |

| 1.1      | Jabber detect             | No jabber condition                        | Jabber condition detected                     | RO                  | LH              | 0                    |     |

| 1.0      | Extended capability       | N/A                                        | Always 1: PHY has extended capabilities       | RO                  | —               | 1                    |     |

| Register | 2 - PHY Identifier        | L                                          |                                               |                     | 1 1             |                      |     |

| 2.15     | OUI bit 3   c             | N/A                                        | N/A                                           | CW                  | -               | 0                    | 0   |

| 2.14     | OUI bit 4   d             | N/A                                        | N/A                                           | CW                  | -               | 0                    |     |

| 2.13     | OUI bit 5   e             | N/A                                        | N/A                                           | CW                  | _               | 0                    |     |

| 2.12     | OUI bit 6   f             | N/A                                        | N/A                                           | CW                  | _               | 0                    |     |

| 2.11     | OUI bit 7   g             | N/A                                        | N/A                                           | CW                  | -               | 0                    | 0   |

| 2.10     | OUI bit 8   h             | N/A                                        | N/A                                           | CW                  | _               | 0                    |     |

| 2.9      | OUI bit 9   I             | N/A                                        | N/A                                           | CW                  | _               | 0                    |     |

| 2.8      | OUI bit 10   j            | N/A                                        | N/A                                           | CW                  | -               | 0                    | 1   |

| 2.7      | OUI bit 11   k            | N/A                                        | N/A                                           | CW                  | _               | 0                    | 1   |

| 2.6      | OUI bit 12   I            | N/A                                        | N/A                                           | CW                  | -               | 0                    | 1   |

| 2.5      | OUI bit 13   m            | N/A                                        | N/A                                           | CW                  | _               | 0                    | 1   |

| 2.4      | OUI bit 14   n            | N/A                                        | N/A                                           | CW                  | _               | 1                    | 1   |

| Bit      | Definition                           | When Bit = 0                | When Bit = 1         | Access <sup>2</sup> | SF <sup>2</sup> | Default <sup>3</sup> | Hex |

|----------|--------------------------------------|-----------------------------|----------------------|---------------------|-----------------|----------------------|-----|

| 2.3      | OUI bit 15   o                       | N/A                         | N/A                  | CW                  | -               | 0                    | 5   |

| 2.2      | OUI bit 16   p                       | N/A                         | N/A                  | CW                  | -               | 1                    |     |

| 2.1      | OUI bit 17   q                       | N/A                         | N/A                  | CW                  | -               | 0                    |     |

| 2.0      | OUI bit 18   r                       | N/A                         | N/A                  | CW                  | -               | 1                    |     |

| Register | 3 - PHY Identifier                   |                             | 1                    | I                   |                 |                      |     |

| 3.15     | OUI bit 19   s                       | N/A                         | N/A                  | CW                  | -               | 1                    | F   |

| 3.14     | OUI bit 20   t                       | N/A                         | N/A                  | CW                  | -               | 1                    |     |

| 3.13     | OUI bit 21   u                       | N/A                         | N/A                  | CW                  | -               | 1                    |     |

| 3.12     | OUI bit 22   v                       | N/A                         | N/A                  | CW                  | -               | 1                    |     |

| 3.11     | OUI bit 23   w                       | N/A                         | N/A                  | CW                  | -               | 0                    | 4   |

| 3.10     | OUI bit 24   x                       | N/A                         | N/A                  | CW                  | -               | 1                    |     |

| 3.9      | Manufacturer's Model<br>Number bit 5 | N/A                         | N/A                  | CW                  | -               | 0                    |     |

| 3.8      | Manufacturer's Model<br>Number bit 4 | N/A                         | N/A                  | CW                  | -               | 0                    |     |

| 3.7      | Manufacturer's Model<br>Number bit 3 | N/A                         | N/A                  | CW                  | -               | 0                    | 5   |

| 3.6      | Manufacturer's Model<br>Number bit 2 | N/A                         | N/A                  | CW                  | -               | 1                    |     |

| 3.5      | Manufacturer's Model<br>Number bit 1 | N/A                         | N/A                  | CW                  | -               | 0                    |     |

| 3.4      | Manufacturer's Model<br>Number bit 0 | N/A                         | N/A                  | CW                  | -               | 1                    |     |

| 3.3      | Revision Number bit 3                | N/A                         | N/A                  | CW                  | -               | 0                    | 0   |

| 3.2      | Revision Number bit 2                | N/A                         | N/A                  | CW                  | -               | 0                    |     |

| 3.1      | Revision Number bit 1                | N/A                         | N/A                  | CW                  | -               | 0                    |     |

| 3.0      | Revision Number bit 0                | N/A                         | N/A                  | CW                  | -               | 0                    |     |

| Register | 4 - Auto-Negotiation Ac              | lvertisement                |                      |                     | 1 1             |                      | 1   |

| 4.15     | Next Page                            | Next page not supported     | Next page supported  | R/W                 | -               | 0                    | 0   |

| 4.14     | IEEE reserved                        | Always 0                    | N/A                  | CW                  | _               | 0†                   | _   |

| 4.13     | Remote fault                         | Locally, no faults detected | Local fault detected | R/W                 | -               | 0                    |     |

| 4.12     | IEEE reserved                        | Always 0                    | N/A                  | CW                  | _               | 0†                   | -   |

| 4.11     | IEEE reserved                        | Always 0                    | N/A                  | CW                  | _               | 0†                   | 1   |

| 4.10     | IEEE reserved                        | Always 0                    | N/A                  | CW                  | -               | 0†                   | 1   |

| 4.9      | 100Base-T4                           | Always 0. (Not supported.)  | N/A                  | CW                  | -               | 0                    |     |

| 4.8      | 100Base-TX, full duplex              | Do not advertise ability    | Advertise ability    | R/W                 | _               | 1                    | 1   |

| Bit     | Definition                 | When Bit = 0                     | When Bit = 1                     | Access <sup>2</sup> | SF <sup>2</sup> | Default <sup>3</sup> | Hex |

|---------|----------------------------|----------------------------------|----------------------------------|---------------------|-----------------|----------------------|-----|

| 4.7     | —                          | _                                | _                                | R/W                 | -               | 1                    | Е   |

| 4.6     | 10Base-T, full duplex      | Do not advertise ability         | Advertise ability                | R/W                 | -               | 1                    |     |

| 4.5     | —                          | —                                | —                                | R/W                 | -               | 1                    |     |

| 4.4     | Selector Field bit S4      | IEEE 802.3-specified default     | N/A                              | CW                  | -               | 0                    |     |

| 4.3     | Selector Field bit S3      | IEEE 802.3-specified default     | N/A                              | CW                  | _               | 0                    | 1   |

| 4.2     | Selector Field bit S2      | IEEE 802.3-specified default     | N/A                              | CW                  | -               | 0                    |     |

| 4.1     | Selector Field bit S1      | IEEE 802.3-specified default     | N/A                              | CW                  | -               | 0                    |     |

| 4.0     | Selector Field bit S0      | N/A                              | IEEE 802.3-specified default     | CW                  | -               | 1                    |     |

| Registe | r 5 - Auto-Negotiation Lir | nk Partner Ability               | -                                |                     |                 |                      | -   |

| 5.15    | Next Page                  | Next Page disabled               | Next Page enabled                | RO                  | -               | 0                    | 0   |

| 5.14    | Acknowledge                | Always 0                         | N/A                              | RO                  | -               | 0                    | -   |

| 5.13    | Remote fault               | No faults detected               | Remote fault detected            | RO                  | -               | 0                    | -   |

| 5.12    | IEEE reserved              | Always 0                         | N/A                              | RO                  | -               | 0†                   | -   |

| 5.11    | IEEE reserved              | Always 0                         | N/A                              | RO                  | -               | 0†                   | 0   |

| 5.10    | IEEE reserved              | Always 0                         | N/A                              | RO                  | -               | 0†                   |     |

| 5.9     | 100Base-T4                 | Always 0. (Not supported.)       | N/A                              | RO                  | -               | 0                    |     |

| 5.8     | 100Base-TX, full duplex    | Link partner is not capable      | Link partner is capable          | RO                  | -               | 0                    |     |

| 5.7     | 100Base-TX, half duplex    | Link partner is not capable      | Link partner is capable          | RO                  | -               | 0                    | 0   |

| 5.6     | 10Base-T, full duplex      | Link partner is not capable      | Link partner is capable          | RO                  | -               | 0                    |     |

| 5.5     | 10Base-T, half duplex      | Link partner is not capable      | Link partner is capable          | RO                  | -               | 0                    |     |

| 5.4     | Selector Field bit S4      | IEEE 802.3 defined.<br>Always 0. | N/A                              | RO                  | -               | 0                    |     |

| 5.3     | Selector Field bit S3      | IEEE 802.3 defined.<br>Always 0. | N/A                              | CW                  | -               | 0                    | 0   |

| 5.2     | Selector Field bit S2      | IEEE 802.3 defined.<br>Always 0. | N/A                              | CW                  | -               | 0                    | 1   |

| 5.1     | Selector Field bit S1      | IEEE 802.3 defined.<br>Always 0. | N/A                              | CW                  | -               | 0                    | 1   |

| 5.0     | Selector Field bit S0      | N/A                              | IEEE 802.3 defined.<br>Always 1. | CW                  | -               | 0                    | 1   |

| Bit      | Definition                                    | When Bit = 0                                 | When Bit = 1                                | Access <sup>2</sup> | SF <sup>2</sup> | Default <sup>3</sup> | Hex |

|----------|-----------------------------------------------|----------------------------------------------|---------------------------------------------|---------------------|-----------------|----------------------|-----|

| Register | 6 - Auto-Negotiation Ex                       | pansion                                      |                                             |                     |                 |                      | 1   |

| 6.15     | IEEE reserved                                 | Always 0                                     | N/A                                         | CW                  | -               | 0†                   | 0   |

| 6.14     | IEEE reserved                                 | Always 0                                     | N/A                                         | CW                  | -               | 0†                   |     |

| 6.13     | IEEE reserved                                 | Always 0                                     | N/A                                         | CW                  | _               | 0†                   | _   |

| 6.12     | IEEE reserved                                 | Always 0                                     | N/A                                         | CW                  | _               | 0†                   | _   |

| 6.11     | IEEE reserved                                 | Always 0                                     | N/A                                         | CW                  | -               | 0†                   | 0   |

| 6.10     | IEEE reserved                                 | Always 0                                     | N/A                                         | CW                  | -               | 0†                   |     |

| 6.9      | IEEE reserved                                 | Always 0                                     | N/A                                         | CW                  | -               | 0†                   |     |

| 6.8      | IEEE reserved                                 | Always 0                                     | N/A                                         | CW                  | -               | 0†                   |     |

| 6.7      | IEEE reserved                                 | Always 0                                     | N/A                                         | CW                  | _               | 0†                   | 0   |

| 6.6      | IEEE reserved                                 | Always 0                                     | N/A                                         | CW                  | _               | 0†                   |     |

| 6.5      | IEEE reserved                                 | Always 0                                     | N/A                                         | CW                  | -               | 0†                   |     |

| 6.4      | Parallel detection fault                      | No Fault                                     | Multiple technologies detected              | RO                  | LH              | 0                    |     |

| 6.3      | Link partner Next Page able                   | Link partner is not Next<br>Page able        | Link partner is Next Page able              | RO                  | -               | 0                    | 4   |

| 6.2      | Next Page able                                | Local device is not Next<br>Page able        | Local device is Next Page able              | RO                  | -               | 1                    |     |

| 6.1      | Page received                                 | Next Page not received                       | Next Page received                          | RO                  | LH              | 0                    |     |

| 6.0      | Link partner<br>Auto-Negotiation able         | Link partner is not<br>Auto-Negotiation able | Link partner is<br>Auto-Negotiation able    | RO                  | -               | 0                    |     |

| Register | 7 - Auto-Negotiation Negotiation              | ext Page Transmit                            |                                             |                     |                 |                      |     |

| 7.15     | Next Page                                     | Last Page                                    | Additional Pages follow                     | RW                  | -               | 0                    | 2   |

| 7.14     | IEEE reserved                                 | Always 0                                     | N/A                                         | RO                  | -               | 0†                   |     |

| 7.13     | Message Page                                  | Unformatted Page                             | Message Page                                | RW                  | _               | 1                    |     |

| 7.12     | Acknowledge 2                                 | Cannot comply with<br>Message                | Can comply with Message                     | RW                  | -               | 0                    |     |

| 7.11     | Toggle                                        | Previous Link Code<br>Word was zero          | Previous Link Code Word was one             | RO                  | -               | 0                    | 0   |

| 7.10     | Message code field<br>/Unformatted code field | Bit value depends on the particular message  | Bit value depends on the particular message | RW                  | -               | 0                    |     |

| 7.9      | Message code field<br>/Unformatted code field | Bit value depends on the particular message  | Bit value depends on the particular message | RW                  | -               | 0                    |     |

| 7.8      | Message code field<br>/Unformatted code field | Bit value depends on the particular message  | Bit value depends on the particular message | RW                  | -               | 0                    |     |

IDT® 10BASE-T/100BASE-TX INTEGRATED PHYCEIVER WITH RMII INTERFACE

| Bit      | Definition                                    | When Bit = 0                                | When Bit = 1                                | Access <sup>2</sup> | SF <sup>2</sup> | Default <sup>3</sup> | Hex |

|----------|-----------------------------------------------|---------------------------------------------|---------------------------------------------|---------------------|-----------------|----------------------|-----|

| 7.7      | Message code field<br>/Unformatted code field | Bit value depends on the particular message | Bit value depends on the particular message | RW                  | -               | 0                    | 0   |

| 7.6      | Message code field<br>/Unformatted code field | Bit value depends on the particular message | Bit value depends on the particular message | RW                  | -               | 0                    |     |

| 7.5      | Message code field<br>/Unformatted code field | Bit value depends on the particular message | Bit value depends on the particular message | RW                  | -               | 0                    |     |

| 7.4      | Message code field<br>/Unformatted code field | Bit value depends on the particular message | Bit value depends on the particular message | RW                  | _               | 0                    |     |

| 7.3      | Message code field<br>/Unformatted code field | Bit value depends on the particular message | Bit value depends on the particular message | RW                  | -               | 0                    | 1   |

| 7.2      | Message code field<br>/Unformatted code field | Bit value depends on the particular message | Bit value depends on the particular message | RW                  | _               | 0                    |     |

| 7.1      | Message code field<br>/Unformatted code field | Bit value depends on the particular message | Bit value depends on the particular message | RW                  | -               | 0                    |     |

| 7.0      | Message code field<br>/Unformatted code field | Bit value depends on the particular message | Bit value depends on the particular message | RW                  | _               | 1                    |     |

| Register | 8 - Auto-Negotiation Ne                       | ext Page Link Partner A                     | bility                                      |                     | 1 1             |                      | 1   |

| 8.15     | Next Page                                     | Last Page                                   | Additional Pages follow                     | RO                  | _               | 0                    | 0   |

| 8.14     | IEEE reserved                                 | Always 0                                    | N/A                                         | RO                  | -               | 0†                   | -   |

| 8.13     | Message Page                                  | Unformatted Page                            | Message Page                                | RO                  | -               | 0                    |     |

| 8.12     | Acknowledge 2                                 | Cannot comply with<br>Message               | Can comply with Message                     | RO                  | -               | 0                    |     |

| 8.11     | Toggle                                        | Previous Link Code<br>Word was zero         | Previous Link Code Word was one             | RO                  | -               | 0                    | 0   |

| 8.10     | Message code field<br>/Unformatted code field | Bit value depends on the particular message | Bit value depends on the particular message | RO                  | -               | 0                    |     |

| 8.9      | Message code field<br>/Unformatted code field | Bit value depends on the particular message | Bit value depends on the particular message | RO                  | _               | 0                    |     |

| 8.8      | Message code field<br>/Unformatted code field | Bit value depends on the particular message | Bit value depends on the particular message | RO                  | _               | 0                    |     |

| 8.7      | Message code field<br>/Unformatted code field | Bit value depends on the particular message | Bit value depends on the particular message | RO                  | -               | 0                    | 0   |

| 8.6      | Message code field<br>/Unformatted code field | Bit value depends on the particular message | Bit value depends on the particular message | RO                  | -               | 0                    |     |

| 8.5      | Message code field<br>/Unformatted code field | Bit value depends on the particular message | Bit value depends on the particular message | RO                  | -               | 0                    |     |

| 8.4      | Message code field<br>/Unformatted code field | Bit value depends on the particular message | Bit value depends on the particular message | RO                  | _               | 0                    |     |

| Bit      | Definition                                    | When Bit = 0                                | When Bit = 1                                | Access <sup>2</sup> | SF <sup>2</sup> | Default <sup>3</sup> | Hex |

|----------|-----------------------------------------------|---------------------------------------------|---------------------------------------------|---------------------|-----------------|----------------------|-----|

| 8.3      | Message code field<br>/Unformatted code field | Bit value depends on the particular message | Bit value depends on the particular message | RO                  | -               | 0                    | 0   |

| 8.2      | Message code field<br>/Unformatted code field | Bit value depends on the particular message | Bit value depends on the particular message | RO                  | _               | 0                    |     |

| 8.1      | Message code field<br>/Unformatted code field | Bit value depends on the particular message | Bit value depends on the particular message | RO                  | -               | 0                    |     |

| 8.0      | Message code field<br>/Unformatted code field | Bit value depends on the particular message | Bit value depends on the particular message | RO                  | -               | 0                    |     |

| Register | 9 through 15 - Reserve                        | d by IEEE                                   | 1                                           |                     |                 |                      |     |

| Register | 16 - Extended Control                         | Register                                    |                                             |                     |                 |                      |     |